KENWOOD

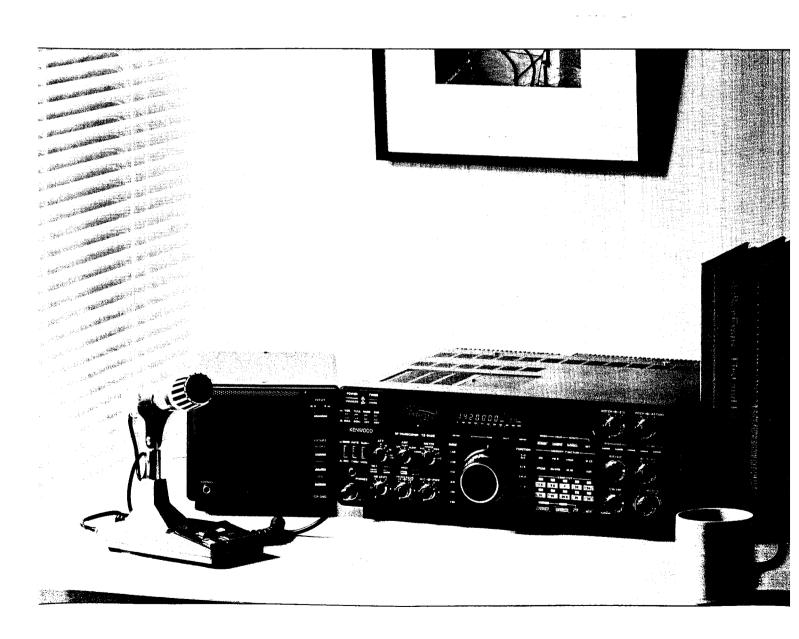

TS-940S

# TECHNICAL INFORMATION

| CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Dogo   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page 3 |

| OUTSTANDING RECEIVER PERFORMANCE AND SENSITIVITY  Super Dynamic Range Receiver Front End/160-m to 10-m Amateur Band Operation with 150-kHz-30 MHz General coverage Receiver/All-Mode Operation/Superb Interference Reduction [(1) SSB I Slope Tuning/ (2) CW VBT (Variable Bandwidth Tuning)/ (3) IF Notch Filter/ (4) AF-Tune/ (5) Narrow/Wide Filter Selection] Built-in CW Variable Pitch Circuit/Dual-Mode Noise Blanker ("Pulse" or "Woodpecker".)/Built-in RIT/XIT/All-Mode Squelch Circuit/RF Attenuator/Switchable AGC Circuit (OFF FAST/SLOW) | to     |

| AUTOMATIC ANTENNA TUNER PLUS LOW DISTORTION, HIGH RELIABILITY TRANSMISSION.  Automatic Antenna Tuner (160-10 meter) Built-in/Low Distortion, High Reliability 28 Volt Powered Final Amplifier/CW Full Break-in/Built-in Speech Processor/RF Output Power Control                                                                                                                                                                                                                                                                                       |        |

| OPERATING FREQUENCY CONTROL USING NEW MICROPROCESSOR PLUS DIGITAL TECHNOLOGY.  10 Hz Step Dual Digital VFO's with Optical Encoder/Built-in Dual VFO A/B Switching System/40 Memory Channels/Built-in Scan Functions/Rapid Band Selection/Keyboard Frequency Selection                                                                                                                                                                                                                                                                                  |        |

| MULTI-FUNCTION MAIN DISPLAY AND SUBDISPLAY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6      |

| MECHANICAL DESIGN AND CONSTRUCTION TYPICAL OF COMPETITION-CLASS EQUIPMENT  Rugged Zinc Die-cast Front Panel and VFO Control Knob/New Highly Efficient Cooling System                                                                                                                                                                                                                                                                                                                                                                                   | 7      |

| A VARIETY OF EXTRA, EASY-TO-OPERATE FUNCTIONS  Built-in AC Power Supply and Speaker/Clock/Timer Function/Transmission Monitor Circuit/High Stability RTTY Transmit Circuit/Optional SO-1 TCXO/Voice Synthesizer Unit (Optional)                                                                                                                                                                                                                                                                                                                        | 7      |

| ADDITIONAL FEATURES, PLUS ACCESSORY TERMINALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7      |

| FREQUENCY CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8      |

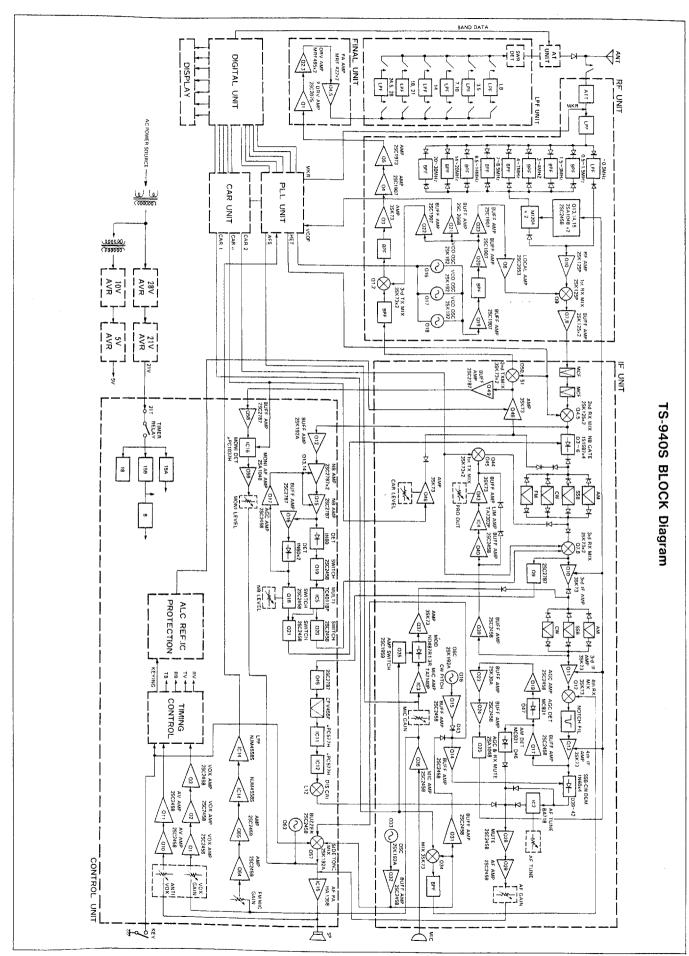

| CIRCUIT DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10     |

| LOCAL OSCILLATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10     |

| RECEIVER  Front end  Additional receiver circuit  Noise blanker (provided on the Control circuit)/CW-VBT, SSB-SLOPE-TUNE (RF/IF and PLL/CAR                                                                                                                                                                                                                                                                                                                                                                                                            | 14     |

| unit)/Notch filter (provided in the IF unit)/AF-TUNE (provided on the IF unit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

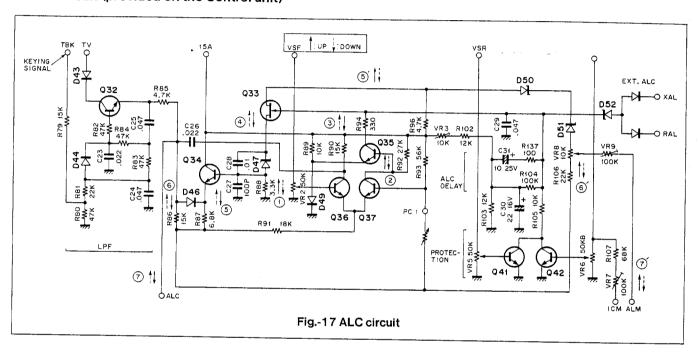

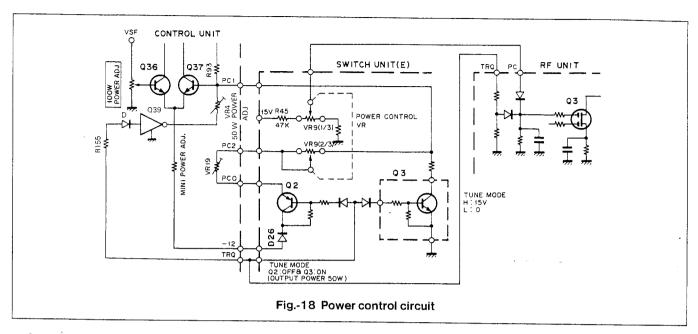

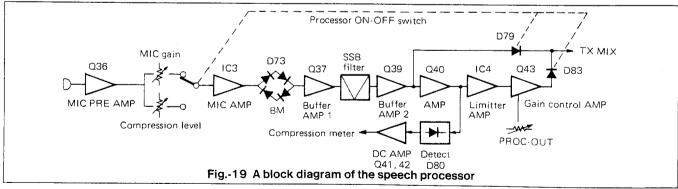

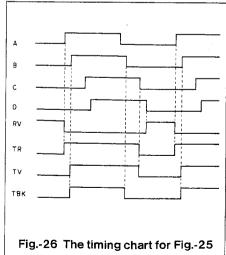

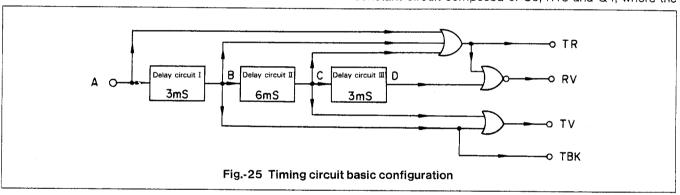

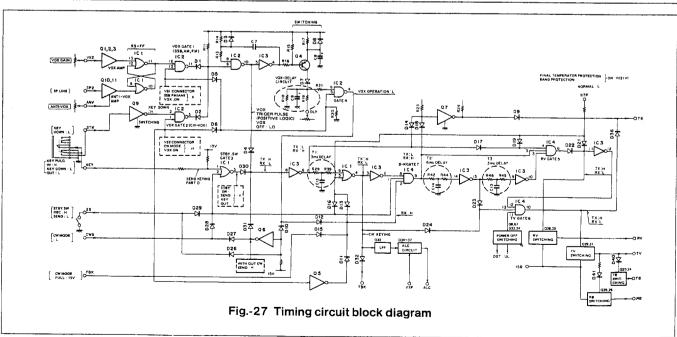

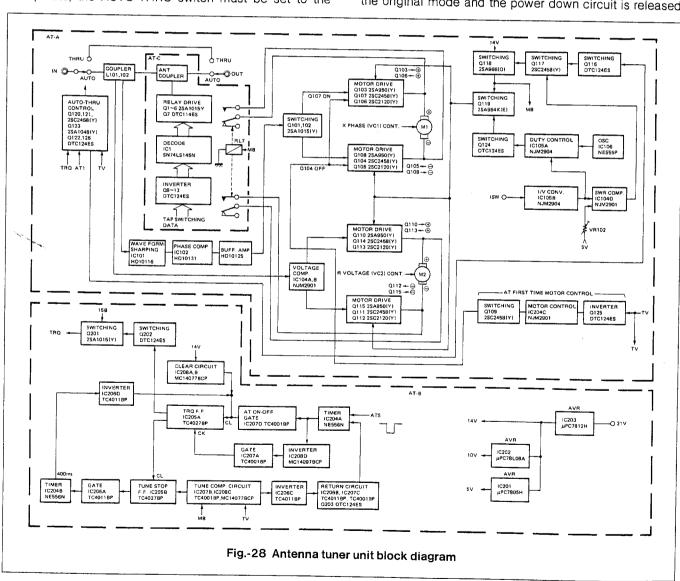

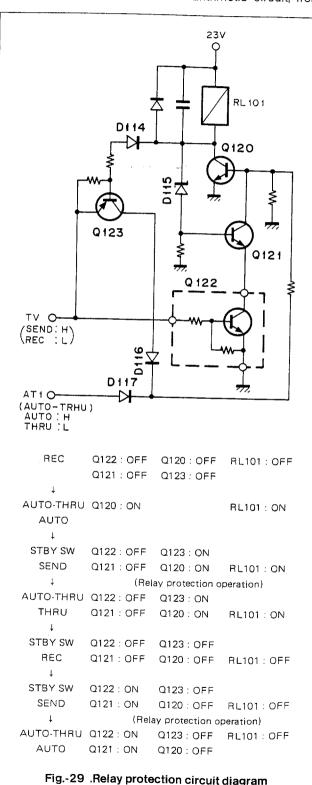

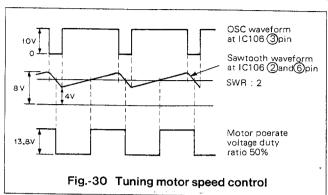

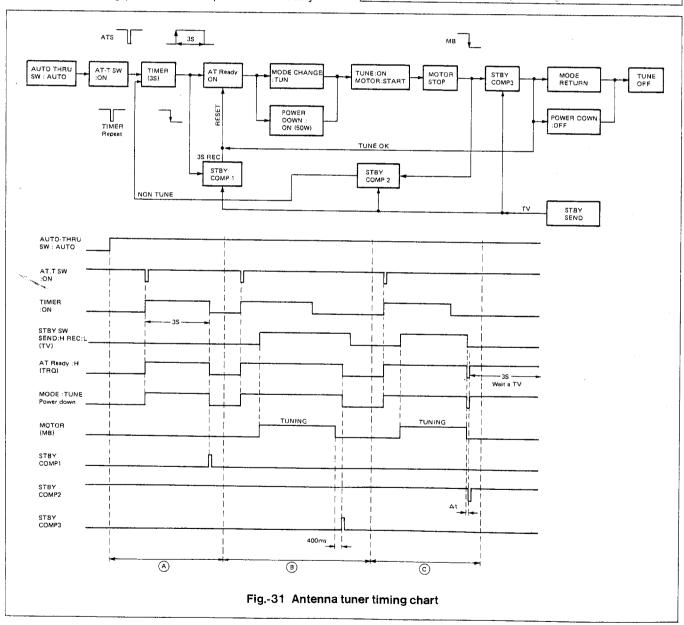

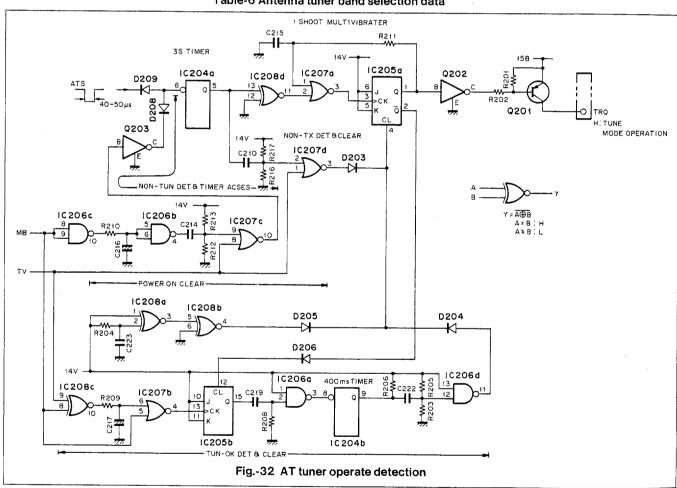

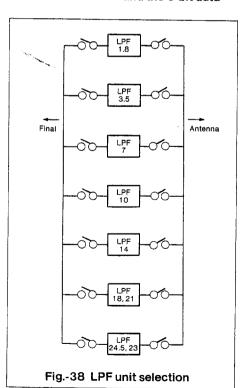

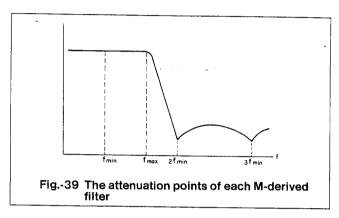

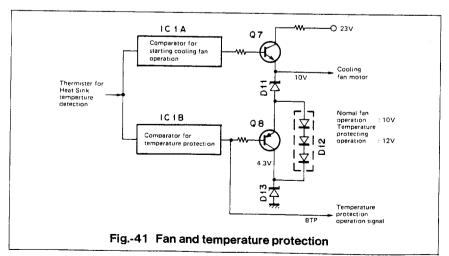

| TRANSMITTER  Additional transmitter circuit  ALC circuit (provided on the Control unit)/Power control/Speech processor (provided on the IF unit)/Monitor circuit (provided on the Control unit)/Timing circuit/VOX, ANTI-VOX circuit (provided on the Control unit)/Antenna tuner/Final amplifier circuit/Final Amplifier Circuit/Final cooling fan driving circuit (provided on the Filter unit)/Final temperature protection circuit (provided on the Filter unit)                                                                                   |        |

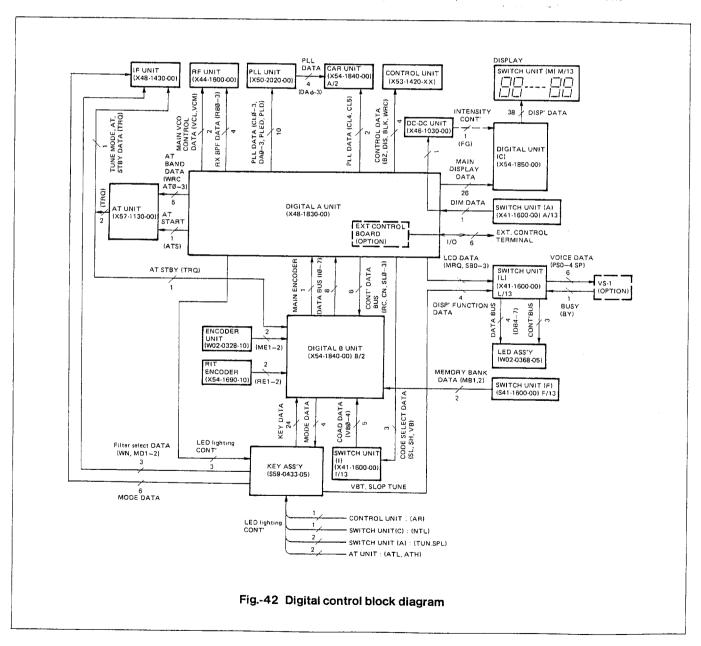

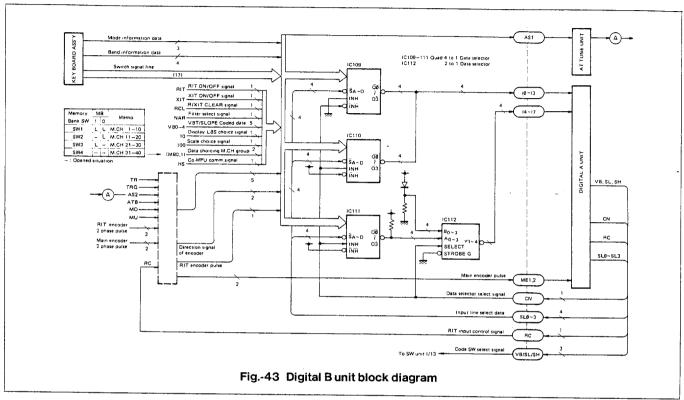

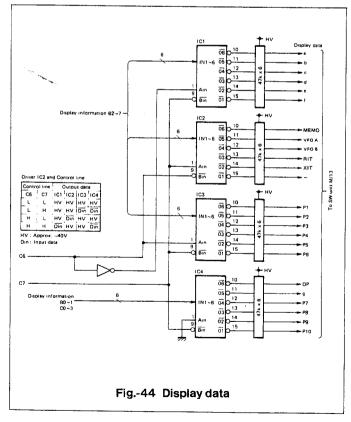

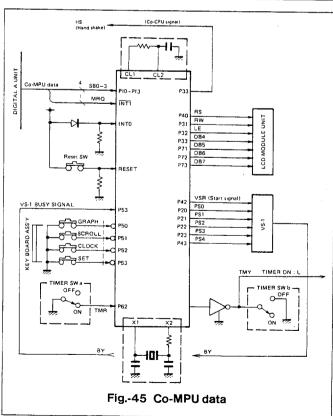

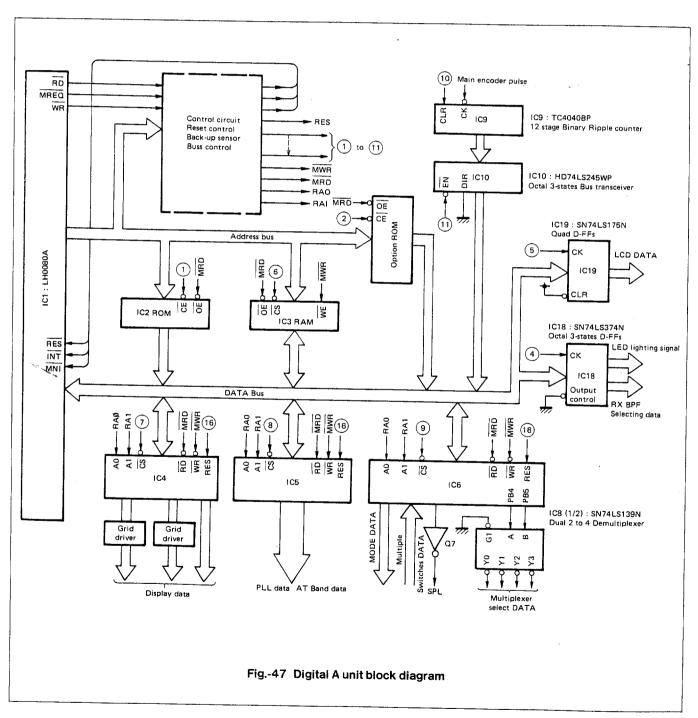

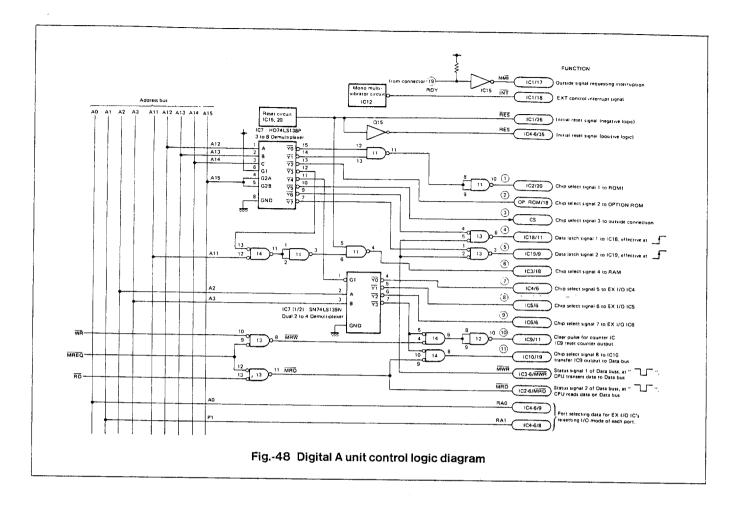

| DIGITAL CIRCUIT  Digital B circuit/Digital C circuit/DC-DC unit/Main Encoder ass'y and RIT Encoder unit/Switch unit/Digital A unit                                                                                                                                                                                                                                                                                                                                                                                                                     | 33     |

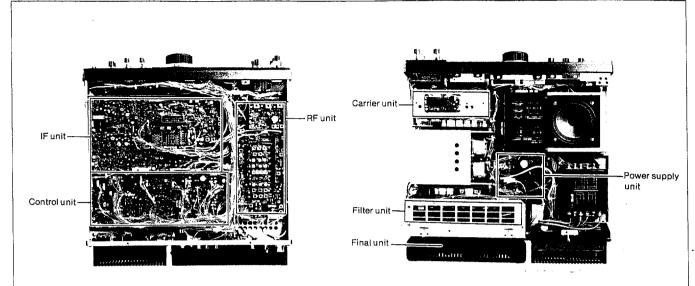

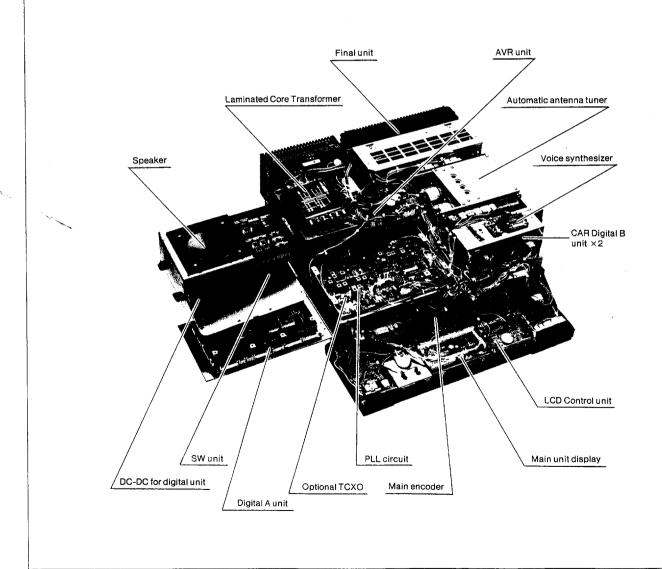

| MECHANICAL DESIGN AND CONSTRUCTION  Panel layout/VFO mechanism/RIT/XIT mechanics/Construction/Highly Efficient, Ducted Air-Flow, Cooling System for the Final and Power Supply unit/Automatic antenna tuner                                                                                                                                                                                                                                                                                                                                            |        |

| OPTIONAL ACCESSORIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 41     |

| SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ΛF     |

#### DX'cellence!!

TRIO-KENWOOD is a multi-national, high-technology company with annual sales in the hundreds of millions of dollars. Founded in 1946, it has come to be recognized all over the world as a producer of the highest quality, most technologically advanced electronics equipment.

TRIO-KENWOOD produces a broad line of amateur radio and land mobile radio products, home video equipment, the finest quality home and car stereo, and a complete line of electronic test equipment, including state-of-the-art solid-state wide band oscilloscopes.

TRIO-KENWOOD enjoys a strong position of leadership, based on a long history of involvement in the design and production of the highest quality amateur radio products. Our engineering department is always hard at work developing new concepts, especially in the field of digital technology and basic performance. Quickly recognizing the tremendous potential for product sophistication through the application of its digital know-how, TRIO-KENWOOD developed a new, state-of-the-art competition class HF transceiver, the TS-940S. The TS-940S has every conceivable feature, and is designed for SSB, CW, AM, FM and FSK operation on all amateur bands, 160 through 10 meters. It incorporates an outstanding 150 kHz to 30 MHz general coverage receiver having superior dynamic range.

### **FEATURES**

# OUTSTANDING RECEIVER PERFORMANCE AND SENSITIVITY.

#### Superior Dynamic Range Receiver Front End.

The TS-940S RF circuits have been specifically designed to provide the lowest noise floor level coupled with a superior dynamic range. Use of 2SK125 junction-type FET's wired in a cascode amplifier circuit, followed by two 2SK125's each in the first balanced mixer and in the push-pull source follower buffer amplifier, and working into a 2nd balanced mixer circuit, results in outstanding two signal characteristics accompanied by a substantially improved noise floor level.

# 160-m to 10-m Amateur Band Operation with 150kHz to 30 MHz General Coverage Receiver.

The TS-940S covers all Amateur bands from 160 to 10 meters, including the new WARC 30, 17, and 12 meter bands. Its general coverage receiver provides reception on any frequency from 150 kHz to 30 MHz. The TRIO-KENWOOD conceived and engineered digital PLL circuit provides superior frequency accuracy and stability since only the standard frequency crystal oscillator determines those parameters. Selection of a specific Amateur band may be speedily and efficiently accomplished by the touch of the appropriate band access key (10 keys provided), or through use of the UP/DOWN

1 MHz step band switches, allowing easy access to all frequencies in the 150 kHz to 30 MHz range. Each of the two digital VFO's is continuously tunable from band to band across the full range of the transceiver.

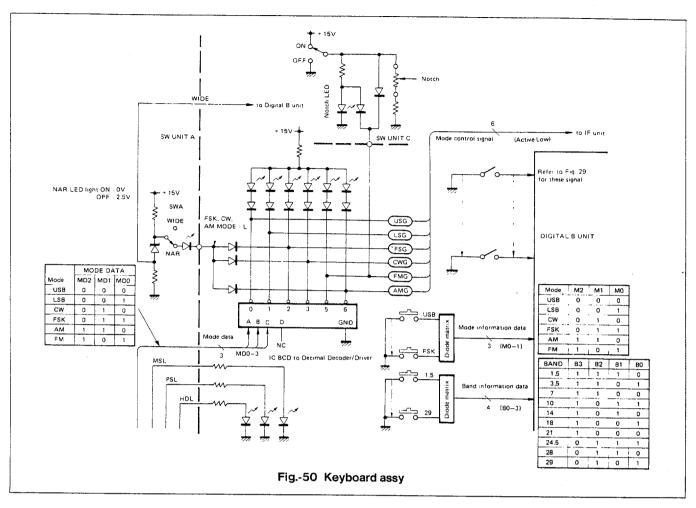

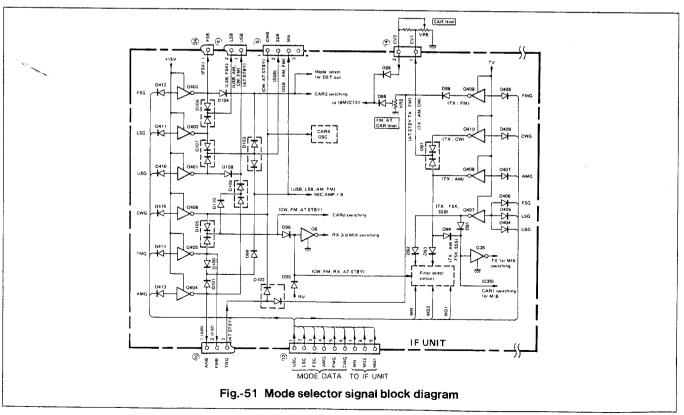

#### All-Mode Operation.

Modes of operation include USB, LSB, CW, AM, FM, and FSK. Mode selection is quickly effected through use of the proper front panel mode key. An adjacent LED confirms the selection. When a key is depressed, the first letter of the mode selected is announced in Morse code, through the internal speaker, e.g., "L" for LSB, "F" for FM, etc. When

FSK is selected, the Morse code letter "R" (for RTTY) is heard.

#### Superb Interference Reduction.

The TS-940S incorporates a number of special interference control circuits perfected by TRIO-KENWOOD and described in the following, that give the operator maximum capability to minimize the effect of interference of all kinds.

#### (1.) SSB IF Slope Tuning.

This feature operates in the LSB and USB modes. Front panel controls are provided to allow independent adjustment of either the low frequency or high frequency slopes of the IF passband. These HIGH CUT and LOW CUT controls permit the operator to easily and quickly define the most ideal IF passband width consistent with readability and interference rejection, and based on conditions as they exist at the time of the contact. The settings of the controls may be graphically illustrated on the LCD sub-display panel.

#### (2.) CW VBT (Variable Bandwidth Tuning.)

When all optional filters are installed, CW VBT operates in the CW, FSK, and AM modes. When none of the optional filters are installed, CW VBT operates in the CW and FSK modes with the filter switch positioned at WIDE, and in the AM mode with the filter switch positioned at NARROW. In the CW mode of operation, the CW VBT and pitch control circuits are automatically enabled. The VBT control allows the passband width to be continuously varied within the

range of the control without affecting the center frequency. Graphic illustration of these adjustements is accomplished on the LCD sub-display panel.

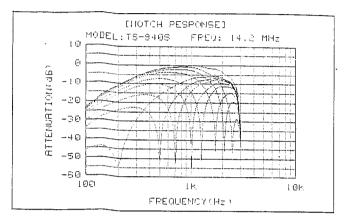

#### (3.) IF Notch Filter.

A tunable notch filter is located between the 4th receive mixer and the 100 kHz IF amplifier. The use of L-C-R components in a bridged-T filter circuit at the 100-kHz IF frequency results in deep, sharp notch characteristics that provide attenuation on the order of 40 dB to the interfering signal. This filter operates in all mode (except FM mode).

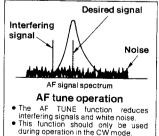

#### (4.) AF-Tune.

The AF-Tune operates to reduce interfering signals and white noise, providing a peak tuning characteristic for the AF frequency response. When the front panel "AF-Tune" switch is depressed to the "ON" position, the "AF-Tune" circuit is activated, allowing operation only in the CW mode. The circuit consists of a three pole active filter located between the SSB/CW demodulator and the AF amplifier. It is tunable to a center frequency of 800 Hz, variable ±400 Hz or greater.

#### (5.) Narrow/Wide Filter Selection.

A front panel "NAR/WIDE" switch allows narrow/wide IF filter selection as required, based on interference conditions.

#### Built-in CW Variable Pitch Circuit.

The CW pitch control shifts the 4th IF passband in the demodulator circuit while, at the same time, raising or lowering the pitch of the audible beat frequency. This is very useful in avoiding interference or for changing the pitch tone to a frequency that is easier to copy.

# Dual-Mode Noise Blanker ("Pulse" or "Woodpecker".)

The noise blanker consists of two circuits, NB-1 and NB-2, each actuated by its own front panel switch. The NB level control adjusts the threshold level of the noise amplifier, allowing the operator to control the effectiveness of the noise blanker under the specific noise and signal level conditions. Depressing the "NB1" switch is most effective in suppressing pulse-type (ignition) noise. Depressing the

NB2 switch is most effective in suppressing noise of a longer duty cycle nature, such as the so-called "woodpecker" type of interference. The threshold level in the NB2 position is factory optimized for maximum effectiveness with minimum degradation of the desired signal. The noise blanker circuitry is also used to suppress "clicks" sometimes introduced by the step reset pulse of the digital VFO's.

#### Built-in RIT/XIT.

The front panel "RIT" (Receiver Incremental Tuning)/"XIT" (Transmitter Incremental Tuning) control shifts the receive or transmit frequency in 10 Hz steps across a range of  $\pm 9.99$  kHz, using an optical encoder, to tune sations that are slightly off frequency, without affecting the VFO transmit/ receive frequency. RIT/XIT frequency shifts are displayed in the main display area. A "CLEAR" switch resets the RIT/XIT frequency to zero. The "RIT/XIT" control may be used in any mode of operation.

#### All-Mode Squelch Circuit.

The squelch circuit is effective in suppressing background noise in all operating modes during key-up intervals.

#### RF Attenuator.

The meticulously engineered receiver section front end includes a 4-step, (0, 10, 20 or 30 dB) RF attenuator, for optimum rejection of intermodulation distortion.

#### Switchable AGC Circuit (OFF/FAST/SLOW).

The automatic gain control (AGC) is activated by a 3-position (OFF/FAST/SLOW) switch, to provide optimum receiver operation in SSB and CW of operation, and under all signal strength conditions.

# AUTOMATIC ANTENNA TUNER PLUS LOW DISTORTION, HIGH RELIABILITY TRANSMISSION.

# Automatic Antenna Tuner (160-10 meters) Built-in.

The TS-940S is available with a completely automatic antenna tuner covering all Amateur bands from 160 through 10 meters built-in, or may be ordered without the tuner installed. The AT-940 antenna tuner is available for future installation in transceivers initially ordered without the automatic antenna tuner.

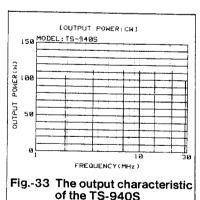

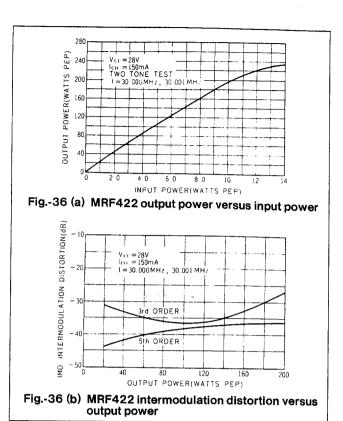

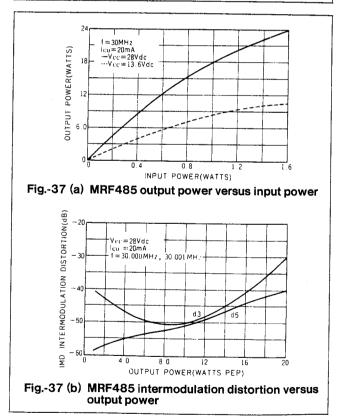

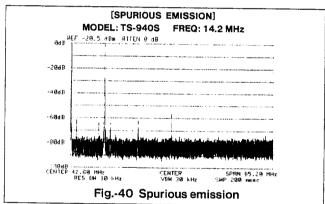

# Low Distortion, High Reliability 28 Volt Powered Final Amplifier.

Through the use of a 28 volt power source, the quality of the transmitted signal has been measurably improved (3rd order intermodulation distortion less than -37 dB) compared to other contemporary designs. Temperature and VSWR monitoring circuits are incorporated in the final amplifier protection circuit to guard against failure of these important components. Continuous operation in the CW or RTTY modes of operation is possible, due to the oversize

heatsink design coupled with the new, super-quiet, ducted cooling system with two speed fans.

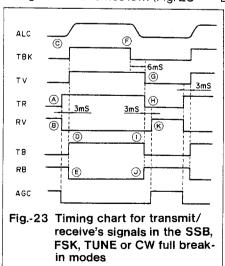

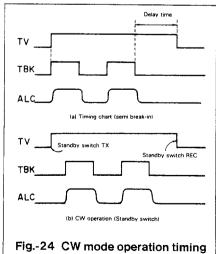

#### CW Full Break-in.

A full break-in capability allows the DX or contest operator to respond more quickly to the calling station. To the "ragchewer", it means a more natural conversation. This capability is made possible through use of CMOS IC's in the timing logic circuitry. The actual switching is accomplished using a specially constructed; fast-acting reed-type relay, which also serves to eliminate the distracting sounds typical of a conventional relay. A front panel switch permits switching to semi break-in operation.

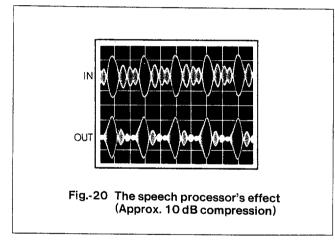

#### Built-in Speech Processor.

The TS-940S employs speech processing circuitry based on RF clipping techniques. A marked improvement in the intelligibility threshold is attainable, depending on the positions of separate front panel "IN" and "OUT" controls. A higher average "talkpower" plus the improved intelligibility makes for outstanding DX performance.

#### **RF Output Power Control.**

Using a front panel control, the RF output power may be continuously varied from 10 watts to the maximum power, in any mode of operation.

# OPERATING FREQUENCY CONTROL USING NEW MICROPROCESSOR PLUS DIGITAL TECHNOLOGY.

The use of a new microprocessor plus advanced digital technology to control the various tuning functions, including the 2 digital VFO's, the 40 channels of memory, band scan and memory scan, etc., assure maximum flexibility and ease of operation under the most difficult operating conditions.

# 10 Hz Step Dual Digital VFO's with Optical Encoder.

Special tuning logic, working in conjunction with the basic 10 Hz step, high stability digital VFO design, provides a variable speed tuning characteristic that is directly related to the speed of tuning knob rotation. A large, die-cast tuning knob with molded rubber cover, rotated at normal tuning speeds, results in frequency shift in 10 Hz increments, or 10 kHz per tuning knob revolution. Rotation of the tuning control at speeds in excess of approximately 2 to 3 revolutions per second causes the tuning step size to be increased proportionally, speeding up the rate of frequency change. Each VFO tunes continuously across the full coverage of the transceiver, utilizing the KENWOOD engineered special optical encoder tuning system.

#### Built-in Dual VFO A/B Switching System.

An "A/B" switch allows the operator to specify the VFO to be used. A "SPLIT" switch is available for split frequency operations. An "A=B" switch makes it possible to quickly duplicate the tuning data (frequency, mode, RIT data) programmed into the active VFO, in the data banks of the inactive VFO. A "T-F SET" switch is provided to permit reversal of the transmit and receive frequencies during split frequency operations. All of these switches are front panel mounted.

#### 40 Memory Channels.

The 40 memory channels are divided into 4 groups of 10 channels each, for operating purposes. Both mode and frequency data are stored, making all operations simple and convenient. The operator may select any 1 of the 4 memory groups for operations, using the 4 position memory bank switch located on the top panel. Depressing the "VFO/M" switch on the front panel permits selection of the memory channel, using the 10 band keys. The "M VFO" switch is used to transfer memory data (frequency, mode) to the active VFO. Memory information is backed-up by an internal lithium battery. (Est. 5 yr. life.)

#### **Built-in Scan Functions.**

Memory scan is initiated by depressing the "MS" switch. Memories in which no data is stored are skipped. Programmable band scan is initiated by depressing the "PG.S" switch, and scans in 10 Hz (100 Hz in AM, FM modes) steps from the lowest frequency within the frequency limits specified in memory channels "9" and "0". A "HOLD" switch is provided to interrupt the scanning process during memory and program scan operations. When the "HOLD" switch has been depressed during program scan, the VFO operating frequency may be adjusted within the frequency limits established in memory channels "9" and "0".

#### Rapid Band Selection.

The specific Amateur band may be quickly selected by depressing the appropriate front panel band key. 1-MHz step "UP" and "DOWN" switches on the front panel or on

the microphone allow rapid selection of tuning frequency for general coverage. An "F.LOCK" switch prevents accidental loss of the selected frequency.

#### **Keyboard Frequency Selection**

The VFO frequency may be directly entered using the front panel number keys. Simply press the "ENT" key, followed by the desired frequency.

## MULTI-FUNCTION MAIN DISPLAY AND SUB-DISPLAY.

The TS-940S incorporates a large fluorescent tube digital display with a unique analog-type sub-scale, plus a new dot-matrix LCD sub-display that displays alpha-numeric information and graphic characteristics.

#### Large Fluorescent Tube Digital Main Display.

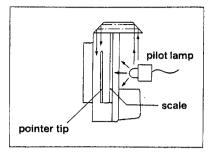

The large, built-in, multi-function fluorescent tube display and its analog-type sub-scale provides improved readability and allows increased operating ease. Transmit/receive frequencies appear on a 7 numeral digital display/analog sub-scale combination, indicating tuning across a selected 1 MHz/100 kHz band segment in 20 kHz/2 kHz steps. A red indicator on the analog scale keeps pace with the tuning knob rotation. A separate 2-digit display indicates RIT/XIT frequency shift to ±9.99 kHz. There are also indicators for VFO "A" or "B", memory "ON", memory channel number, "F.LOCK", and RIT/XIT "ON". The use of the fluorescent tube display makes reading easy, and minimizes eye fatigue. A "DIM" switch has been provided to allow dimming the display and the meter illumination, if desired.

#### LCD Dot-matrix Sub-display.

The sub-display is capable of displaying a maximum of 16 digits and 2 lines of data. Frequency, graphic characteristics, messages, and clock time are the 4 different kinds of information that can be displayed.

#### ■ Frequency.

The upper line shows frequency and mode of VFO "B" when VFO "A" is indicated on the main display. The lower line indicates memory group  $(1 \sim 4)$ , memory channel (CH-1, 2, .... 9, 0), plus frequency and mode during VFO operations.

#### ■ Graphic Characteristics.

Graphically indicates the effect on bandwidth when "SSB SLOPE TUNE" or "CW VBT" controls are operated.

#### Messages.

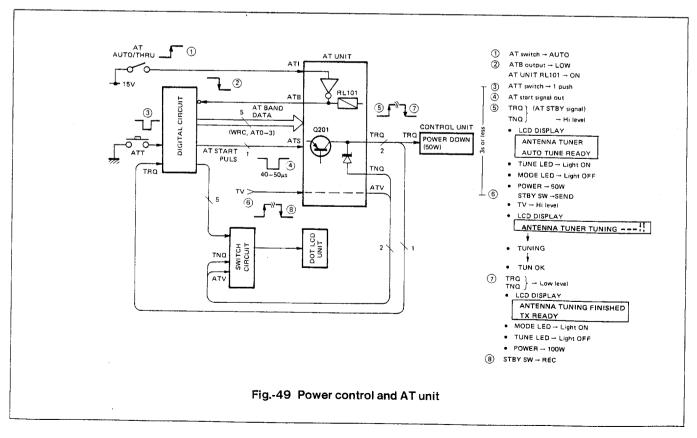

Displays messages relating to operation of the Automatic Antenna Tuner, as follows:

- 1. "ANTENNA TUNER AUTO TUNE READY" when "AT.T" switch is depressed.

- "ANTENNA TUNER TUNING" when the transmitter is keyed within 3 seconds after pressing "AT.T" switch.

3. "TUNING FINISHED TX-READY" when automatic antenna tuner has finished tuning.

#### Clock.

Indicates the current time, or the preset timer time. The clock has a built-in battery back up. (Est. 3 yr. life)

# MECHANICAL DESIGN AND CONSTRUCTION TYPICAL OF COMPETITION-CLASS EQUIPMENT.

# Rugged Zinc Die-cast Front Panel and VFO Control Knob.

The Zinc die-cast front panel assures maximum mechanical stability under even the most severe operating conditions. The large die-cast VFO control knob, with a textured rubber cover provides a positive tuning "feel" coupled with a strong flywheel effect, further enhancing the unit's flexibility of use and ease of operation.

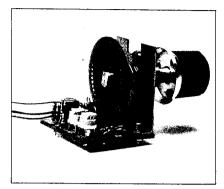

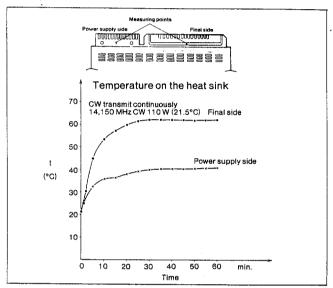

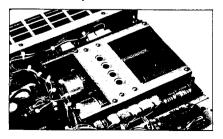

#### New Highly Efficient Cooling System.

The 100 W final amplifier stage is mounted directly on its die-cast aluminum heat sink, providing maximum thermal conduction efficiency. The high efficiency of the cooling system permits continuous transmission at full power for periods of exceeding one hour without thermal shut-down. The power supply unit has its own independent cooling system.

# A VARIETY OF EXTRA, EASY-TO-OPERATE FUNCTIONS.

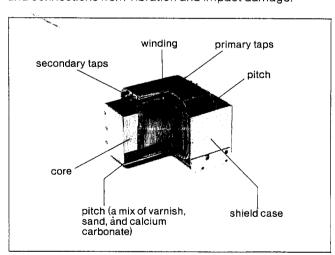

#### Built-in AC Power Supply and Speaker.

The TS-940S is a self-contained HF station, including a built-in power supply, and a rugged, top-mounted, high quality, 10 cm (4 inch) speaker. The power supply circuit provides ample capacity thru the use of a special, compact, laminated core transformer, assuring maximum stability of operation in the final transistor circuits. The correct AC circuit polarity is achieved through use of the 3-wire connector and cable assembly supplied with the unit.

#### Clock/Timer Function.

In addition to a 24-hour clock function, a single event timer is provided for scheduled un-attended recording of a specified transmission. Clock/Timer program data may be displayed on the LCD sub-display at the operator's option.

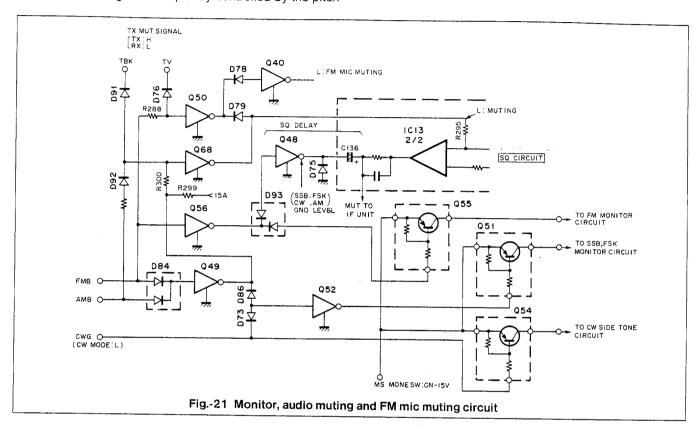

#### **Transmission Monitor Circuit.**

A built-in transmit monitor circuit operating in the SSB, FM, and FSK modes may be operator activated by depressing the front panel "MONI" switch. This circuit monitors the product detector signal from the output of the IF section during transmission, allowing the operator to check his audio quality, and the effectiveness of the speech processor.

#### High Stability RTTY Transmit Circuit.

The stability of RTTY transmissions is greatly improved through design that obtains the FSK signal information from the reference oscillator. The FSK shift width is 170 Hz.

#### Optional SO-1 TCXO.

An optional high stability temperature compensated crystal oscillator may be installed in place of the reference oscillator. This unit operates at 20 MHz with an accuracy of 0.5 ppm between -10 degrees Celsius and +50 degrees Celsius, upgrading the transceiver to a level challenging professional standards.

#### Voice Synthesizer Unit (Optional).

An optional VS-1 "Voice Synthesizer Unit", which announces the operating frequency on demand by depression of the front panel "VOICE" key, is available. Installation within the cabinet is simple and easy.

# ADDITIONAL FEATURES, PLUS ACCESSORY TERMINALS.

#### Dimmer Switch.

A front panel "DIM" switch permits selection of either normal or reduced intensity on the digital display and SWR/POWER meter.

#### 100-kHz Marker.

A 100 kHz marker signal, controlled by a switch located under the sliding panel on top of the unit, is available for use in calibrating the fundamental oscillator against received standards such as WWV or MSF.

#### **VOX Circuit.**

The VOX gain, VOX delay, and Anti-VOX controls are located beneath the sliding panel on the top of the cabinet.

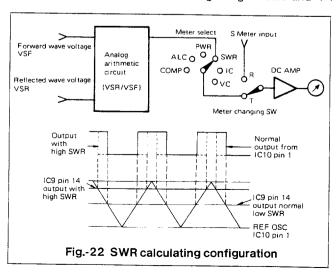

#### Meter Transmission Functions.

"COMP" (Compression), "ALC" (Automatic Level Control), "POWER" (RF Output Power), "SWR" (Standing-wave Ratio), "IC" (Final Amplifier Collector Current), and "VC" (Final Amplifier Collector Voltage.) 5 units and dB on receive.

#### LED Indicators for Miscellaneous Functions.

"ON AIR", "AT", "TUNE", "SPLIT", "NOTCH", "NAR".

#### Input/Output Terminals.

Receiver antenna terminal and switch, transverter terminal, IF OUT 1 (For PAN-DISPLAY) and IF OUT 2 (Oscilloscope Modulation Monitor) terminals, phone patch IN/OUT terminals, accessory terminals 1 and 2, remote control terminal.

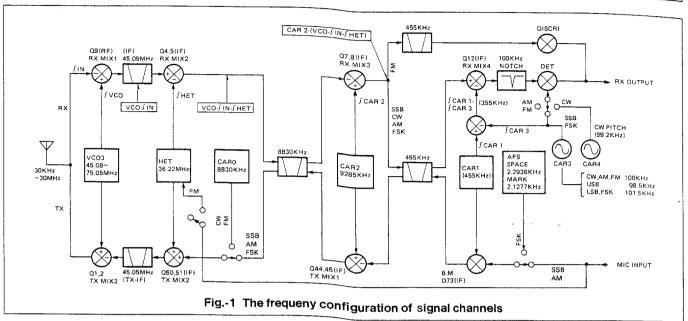

# Frequency configuration

The TS-940S is quadruple conversion in SSB, CW, AM and FSK modes and triple conversion in FM mode. As a transmitter, it is double conversion in CW and FM modes and triple conversion in SSB, AM and FSK modes.

Fig. 1 shows the frequency configuration of the signal channels as both a transmitter and a receiver. The receiver frequency in SSB mode will be described now. It is assumed that the input frequency entered from the antenna is  $f_{IN}$  the local oscillator input of RX MIX1 is  $f_{VCC}$  the local oscillator input of RX MIX2 is  $f_{HET}$  the local oscillator input of RX MIX3 is  $f_{CAR2}$  and the local oscillator input of RX MIX4 is  $f_{CAR1} - f_{CAR3}$ .

When the receiver output tone frequency by  $f_{IN}$  is zero beat (namely, at zero to the SSB signal with a carrier point of  $f_{IN}$ ), the relationship between these signals is expressed by the following equation:

$$\underbrace{\frac{[f_{CAR2} - |(f_{VCO} - f_{IN}) - f_{HET}|] - (f_{CAR1} - f_{CAR3})}{MIX1}}_{MIX2} = f_{CAR3}$$

$$\underbrace{\frac{MIX1}{MIX2}}_{MIX4}$$

The equation is arranged as follows:

$$f_{IN} = f_{VCO} - f_{HET} + f_{CAR1} - f_{CAR2} \qquad (1)$$

The term  $f_{CAR3}$  is eliminated as it is not related to the receiver frequency itself. As for the remaining terms, all are generated in the PLL (Phase Locked Loop) circuit in the configuration shown in Fig. 2. The frequencies generated are now examined for each loop.

In VCO<sub>0</sub>

$$\frac{fvcoo}{N_0} = \frac{\frac{1}{2} \cdot fs_{TD}}{500}$$

$$\therefore fvcoo = \frac{N_0}{1000} \cdot fs_{TD}$$

(2)

In VCO<sub>1</sub>

$$\frac{fvcoo}{N_1} = \frac{\frac{1}{4} \cdot fs_{TD}}{500}$$

$$\therefore fvcoo = \frac{N_0}{N_1} \cdot fs_{TD}$$

(3)

In VCO<sub>2</sub>

$$\frac{fvcoo}{100} \cdot fs_{TD} + \frac{fvcoo}{100} = \frac{\frac{1}{2} \cdot fs_{TD}}{500}$$

$$\therefore fvcoo = \frac{N_0}{1000} \cdot fs_{TD} + \frac{fvcoo}{100} = \frac{fvcoo}{10} = \frac{1}{100} \cdot fvcoo = \frac{fvcoo}{10} = \frac{N_0}{100} \cdot fs_{TD} + \frac{fvcoo}{100} = \frac{fv$$

In VCO<sub>3</sub>

$$\frac{fvco_{2}}{10} + fsr_{D} + 3 \cdot fsr_{D} - fvco_{3}}{N_{3}} = \frac{\frac{1}{2}fsr_{D}}{20}$$

$$\therefore fvco_{3} = \frac{160 - N_{3}}{40} \cdot fsr_{D} + \frac{fvco_{2}}{10}$$

In VCO<sub>4</sub>

$$\frac{fvco_{4}}{N_{4}} = \frac{fc_{P}}{1800} \quad \therefore fvco_{4} = \frac{N_{4}}{1800} \cdot fc_{P}$$

(6)

In VCO<sub>5</sub>

$$\frac{f_{VCO5}}{N_5} = \frac{f_{VB}}{1800}$$

$\therefore f_{VCO5} = \frac{N_5}{1800} \cdot f_{VB}$  (7)

The above equations are thusly arranged so the frequencies of each local oscillator are expressed as follows.

$$f_{VCO} = \left(\frac{160 - N_3}{40} + \frac{N_2}{10000} + \frac{N_1}{2000000}\right) \cdot f_{STD}$$

$$-\frac{N_4}{180000} \cdot f_{CP} - \frac{N_5}{180000} \cdot f_{VB}$$

(8)

$$f_{HET} = f_{VCO0} = \frac{N_0}{1000} \cdot f_{STD} \tag{9}$$

$$f_{CARI} = \frac{1}{100} f_{VCO4} = \frac{N_4}{180000} \cdot f_{CP}$$

(10)

$$f_{CAR2} = \frac{1}{2} f_{STD} - \frac{1}{100} f_{VCO5} = \frac{1}{2} \cdot f_{STD} - \frac{N_5}{180000} \cdot f_{VB}$$

. (11)

$$f_{CAR0} = f_{CAR2} - f_{CAR1} = \frac{1}{2} \cdot f_{STD} - \frac{N_5}{180000} \cdot f_{VB} - \frac{N_4}{180000} \cdot f_{CP}$$

(12)

Therefore, the term " $f_{IN}$ " of equation (1) is re-written as follows.

$$f_{IN} = \left(\frac{160 - N_3}{40} + \frac{N_2}{10000} + \frac{N_1}{2000000} - \frac{N_0}{1000}\right) \cdot f_{STD} \quad ... \quad (13)$$

As shown in equation (13), the receiver frequency is determined only by the reference  $f_{STD}$  and the dividing ratio NO-N3. This shows the following.

- N is the numeric value determined by the microprocessor in accordance with the operating frequency and, essentially, it does not include the error component.

- With the primary term of fstd only, the reference frequency accuracy is directly considered as an operating frequency accuracy.

- 3. The operating frequency does not change even if N4, N5,  $f_{CP}$  and  $f_{VB}$  change.

The accuracy of the reference crystal oscillator used in the TS-940S is 10PPM (-10~+50°C). It is 0.5PPM (-10~+50°C) when the optional TCXO (Temperature Compensated Crystal Oscillator) SO-1 is used.

According to 1 and 2, the overall accuracy of the TS-940S is highly stable with the same value as described above obtainable at any point in the 30 kHz $\sim$ 30 MHz range. Utilizing the characteristic of 3 above, the TS-940S has variable band width functions such as VBT and slope turning controlled by the microprocessor, which operates N4 and N5. At the same time, the TS-940S sets the carrier point by making fine adjustment of  $f_{CP}$  and adjusts the initial setting of VBT by making fine adjustment of  $f_{VB}$ . The receiver frequency in SSB mode has been described. In other modes or when used as a transmitter, likewise, the frequency is determined by the reference  $f_{STD}$  and dividing

ratio

The display frequencies are shown in the following table.:

| USB, LSB | Carrier point frequency        |

|----------|--------------------------------|

| cw       | Transmission carrier frequency |

| AM, FM   | IF filter center frequency     |

| FSK      | Space transmitter frequency    |

Table-1, Display frequencies in each mode

In CW mode, the TS-940S receiving pitch can be changed to the required frequency while the desired signal remains in the center of the IF filter passband. (Variable CW pitch system)

The receiving pitch varies with the transmitter CW side tone. It is thus possible to immediately zerobeat by receiving the desired signal at the same pitch as the side tone. FSK transmission is executed in LSB mode. The audio signal made by dividing the reference frequency

(Space

$$=\frac{f_{STD}}{8720} = 2.2936 \text{ kHz, mark} = \frac{1}{9400} = 2.1277 \text{ kHz}$$

)

is used as the AFSK (Audio Frequency Shift Keying) signal. In FSK mode, unlike the operation is LSB mode, the IF is shifted (the dividing frequency N4 is shifted) for both transmission and reception so that the signal at 2.2936 kHz/2.1277 kHz passes through the center of the IF filter. The  $f_{VCO_1}$  is shifted, since the display frequency is the space transmitter frequency. (The dividing ratio N1 is shifted.)

FM transmission is obtained in this system by modulating the  $f_{HET}$  by applying the audio signal from the microphone to the VCO<sub>0</sub>.

The specifications of each frequency element are as follows.

| fstd 20 MHz            | Standard: ±10 PPM (-10°C~+50°C)                       |

|------------------------|-------------------------------------------------------|

|                        | max.                                                  |

|                        | SO-1 mounted: ±0.5 PPM                                |

|                        | (-10°C~+50°C) max.                                    |

| <i>fcp</i> 9 MHz±∆cp   | $\triangle$ CP = Carrier point adjustment             |

|                        | component                                             |

| <i>fvв</i> 9 MHz±∆νв   | $\triangle VB = VBT$ initial setting adjustment       |

| Dividing ratio         | component                                             |

| <i>N</i> ₀1811         | •                                                     |

| $N_1 10000 \sim 10999$ | Applicable to the display frequency                   |

|                        | 0.00 kHz~9.99 kHz.                                    |

|                        | +229 added in FSK mode.                               |

|                        | Applicable to the display frequencies                 |

|                        | 000.00~490.00 kHz and                                 |

|                        | 500.00~990.00 kHz.                                    |

| $N_2$ 2310 $\sim$ 2555 | (Only the integer multiple of 5 is used)              |

| $N_377 \sim 17$        | Applicable to every multiple of 500 kHz               |

| • • • •                | of 30 kHz~30 MHz                                      |

| $N_4$ 9100 + (Mode sh  | hift) $\pm \triangle 4$ $\triangle 4$ = Variable band |

| USB                    | -30 AM-W, N 0                                         |

| LSB                    | +30 FM 0                                              |

| CW-W                   | -14 FSK-W, N +44                                      |

| CW-N                   | 0                                                     |

| <i>N</i> ₅ 14300±∆5    | $\triangle 5 = Variable band$                         |

# CIRCUIT DESCRIPTION

#### Local oscillator

#### **PLL Circuit**

This is a digital VFO (Variable Frequency Oscillator) to cover a frequency range of from 45.08 MHz ~75.05 MHz in 10 Hz steps, in accordance with the TS-940S operating frequency of 150 kHz ~30 MHz. Three PLL loops are linked in analog mode. The dividing ratio data to each PLL is controlled by the microprocessor.

Each loop is of a single crystal frequency control system: the VCO phase is compared with the unique reference frequency  $f_{STD} \cdot CAR1$  and CAR2 frequencies are inserted halfway in the analog link, enabling variable bandwidth functions such as VBT and slope tuning.

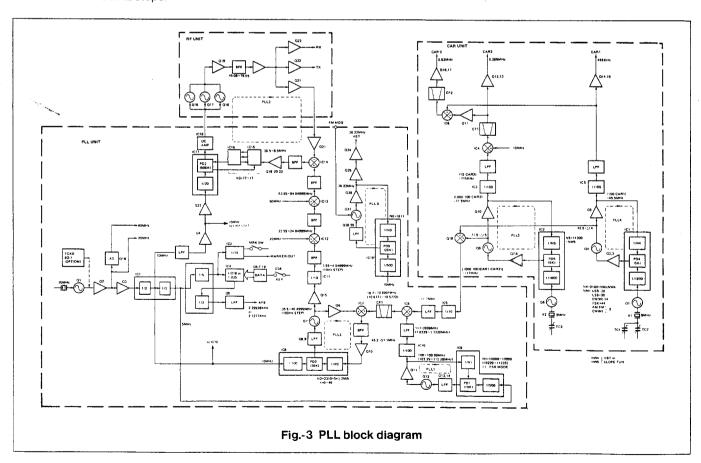

Operation of the PLL circuit is explained with reference to Fig. 3 "PLL block diagram".

The PLL-1 consists mainly of IC9: MN6147. VCO1 of Q12: 2SC2668 is locked in the  $100\sim109.99$  MHz range. The  $1/4~f_{STD}$  (5 MHz) signal is supplied from the reference signal generator to IC9, where it is divided to 1/500 and output as a 10 kHz comparison frequency.

The VCO1 output is applied to the same IC9 via buffer amplifier Q11, where it is divided to 1/N1. The signal is then coupled to the phase comparator, where it is compared with the above 10 kHz signal, and the output locks VCO1 in 10 kHz steps.

As N1, the 1000 steps (10000~10999) of dividing data equivalent to the low order 9.99 kHz width of the operation frequency is sent from the digial A unit to the PLL unit as a 4 bit serial data stream. A microprocessor is used for this data sending operation (DA0—DA3, CK1). In FSK mode, as the space frequency is used as an operating frequency, N1 is shifted to 10229~11228.

The PLL-1 output is divided to 1/100 by IC10: M54459L and becomes a signal of 1 MHz~1.0999 MHz (1.0229~1.1228 MHz in FSK mode) in 100 Hz steps. This signal sent from the PLL-1 channel to IC6: SN16913P, i.e., the signal sent from the PLL-1 channel to IC6 is:

$$\frac{f_{VCO\,1}}{100} = \frac{1}{100} \times \frac{N_{\,1}}{500} \times \frac{1}{4} \cdot f_{STD} = \frac{N_{\,1}}{200000} \cdot f_{STD} \tag{1}$$

On the other hand, the  $f_{VCO4}+f_{VCO5}$  signal (approx. 117 MHz) is sent from the carrier unit to PLL unit. This signal is divided to 1/10 by IC5: HD10551 and applied to the mixer IC6. This signal is expressed by the equation:

$$\frac{1}{10} \cdot (f_{VCO4} + f_{VCO5}) = \frac{1}{10} \left\{ 100 \cdot f_{CAR1} + 100 \left( \frac{1}{2} f_{STD} - f_{CAR2} \right) \right\}$$

$$= 5 \cdot f_{STD} + 10 f_{CAR1} - 10 f_{CAR2} \dots (2)$$

It becomes a signal of approx. 11.7 MHz. Therefore, IC6 output becomes a signal of approx. 10.65 MHz expressed by:

$$5f_{STD} + 10f_{CAR1} - 10f_{CAR2} - \frac{N_1}{200000} \cdot f_{STD}$$

(3)

Any mixer spurious signal is eliminated by ceramic filter CF1: SFJ10.7MA-D and applied to the next PLL-2 loop. PLL-2 consists mainly of IC8: MN6147, which locks the output signal of mixer IC7: SN16913P, which is the VCO2 output of Q7: 2SC2668 and the signal from CF1, in the range of  $46.2 \sim 51.1$  MHz. The  $1/2 f_{STD}$  (10 MHz) signal is supplied from the reference frequency generator to IC8, where it is divided to 1/500 to make a comparison frequency of 20 kHz. The VCO2 output is applied to mixer IC7 via buffer amplifier Q6: 2SC2668 and added to the signal (the configuration of equation (3) = 10.65 MHz) from CF1, and this output is sent to IC8 via a BPF (Band Pass Filter) and amplifier Q10: 2SC2668.

This signal is divided to 1/N2, compared in phase with the above 20 kHz signal and used to control VCO2. This operation is expressed by:

$$\left(f_{VCO2} + 5f_{STD} + 10f_{CAR1} - 10f_{CAR2} - \frac{N_1}{200000} \cdot f_{STD}\right) \times \frac{1}{N_2}$$

$$= \frac{1}{500} \times \frac{1}{2} \cdot f_{STD} \quad .... (4)$$

N2 means to cover the low order 500 kHz width of the operating frequency in 10 kHz steps and takes a numeric value of 50 steps which becomes an integer multiple of 5 in the range 2310~2555. Like N1 in PLL-1, this data is sent by the microproceesor from the digital A unit to the PLL unit as a 4 bit serial data stream. (DA0—DA3, CK2). Therefore, the output signal of PLL-2 is expressed by the equation:

$$f_{VCO2} = \left(\frac{N_1}{200000} + \frac{N_2}{1000} - 5\right) f_{STD} - 10 f_{CAR1} + 10 f_{CAR2} \dots (5)$$

According to the values of N1 and N2, a frequency of 35.5~40.4999 MHz is generated in 100 Hz steps. The PLL-2 output is divided to 1/10 by IC11: HD10551 via buffer amplifier Q15: 2SC2668, and becomes a signal in 10 Hz steps in the 3.55~4.04999 MHz range.

First, fstd (20 MHz) is added in mixer IC12: SN16913P and then, 3.fstd (80 MHz) is added in mixer IC13: SN16913P and the signal is converted to 83.55~84.04999 MHz. As a result, 4.fstd (80 MHz) is added, but such a frequency configuration is employed in order to avoid unwanted mixer spurious components. This signal is applied to mixer IC14, where it is mixed with the final VCO output signal.

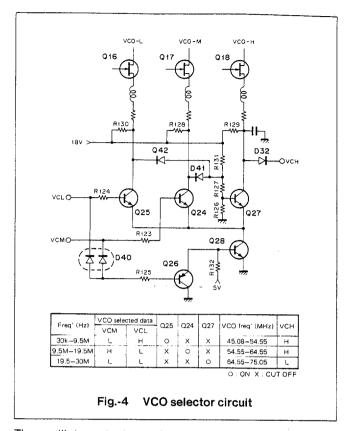

The final VCO is located on the RF unit and consists of three elements: Q16: 2SK192A handling the frequency below 9.5 MHz, Q17: 2SK192A for 9.5~19.5 MHz and Q18: 2SK192A for 19.5 MHz~30 MHz. Each VCO is selected by the VCO select information (VCM or VCL, VCH is derived) sent from the Digital A unit by the microprocessor. The VCO selector circuit is shown in Fig. 4.

The oscillator output runs through the buffer amplifier Q19: 2SC1907 and the high frequency component is eliminated by a BPF. The signal runs through the buffer amplifier Q20: 2SC1907 and is then separated into three channels of buffered output. The Q21: 2SC2668 output is supplied to the PLL unit, composing a final PLL loop. The Q22: 2SC1907 output is applied to the third transmitter mixer. From Q23: 2SC1907, the VCO output is applied to the first receiver mixer via amplifier Q6: 2SC2053.

The signal from the RF unit, final VCO is connected to the PLL unit VCO terminal and is applied to mixer IC14 via buffer amplifier Q21: 2SC2668. Therefore, the mixer output becomes:

$$\frac{f_{VCO2}}{10} + f_{STD} + 3f_{STD} - f_{VCO}$$

$$= \left(\frac{N_1}{2000000} + \frac{N_2}{10000} + \frac{7}{2}\right) f_{STD} - f_{CAR1} + f_{CAR2} - f_{VCO}. . . (6)$$

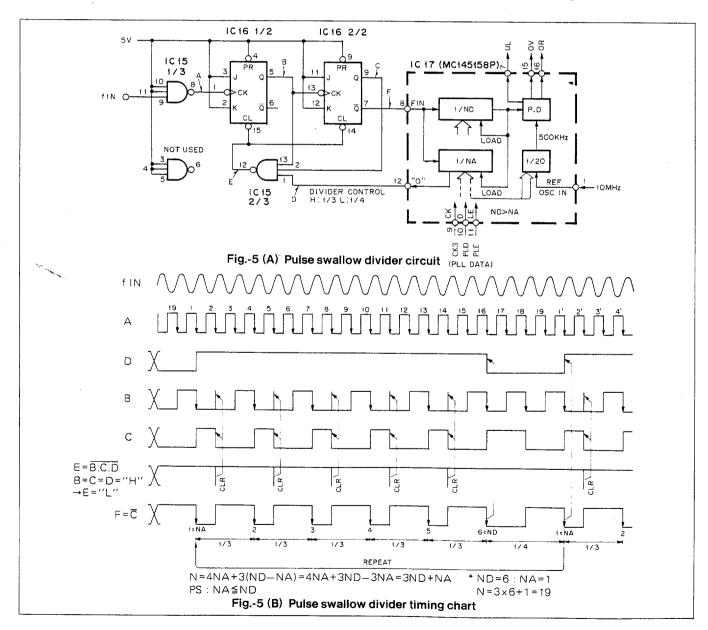

This signal goes through a BPF and is amplified by Q18, 19: 2SC2668, Q20: 2SC1907 and Q22: 2SC2668 and then, the waveform is shaped by IC15-1/3: SN74S10N and applied to 1/3 or 1/4 prescaler IC16: SN74S112N. IC16 is originally a dual function flip-flop circuit and works as a 1/4 divider, but its function is changed to a 1/3 divides by the control signal from the later stage PLL IC17: MC145158, i.e., a pulse swallow divider is composed of IC17 internal divider, IC16 and IC15-1/3.

PLL IC17, the primary element of the final PLL loop PLL-3, is provided with the modulus control function which externally sets both the reference dividing ratio and comparison dividing ratio by serial data, and composes a pulse swallow counter using an external prescaler.

The 1/2 fsrp (10 MHz) signal is supplied from the reference frequency generator to IC16 via buffer amplifier Q23: 2SC2668. The signal is divided to 1/2 in IC16 to make a comparison output frequency of 500 kHz.

The signal supplied from IC14 to the swallow counter via the BPF and amplifier is divided to 1/N3 and compared in phase with the 500 kHz signal in the phase comparator. This controls the RF unit final VCO by the error correction voltage.

The operation is expressed by:

$$\left\{ \left( \frac{N_1}{2000000} + \frac{N_2}{10000} + \frac{7}{2} \right) f_{STD} - f_{CAR1} + f_{CAR2} - f_{VCO} \right\} \times \frac{1}{N_3} = \frac{1}{20} \times \frac{1}{2} f_{STD} \quad \dots \quad (7)$$

N3 means to cover the overall operating frequency range (30 kHz-30 MHz) in 500 kHz steps and becomes 60 steps of 77-17. This data is also sent by the microprocessor from the Digital A unit to the PLL unit as

serial data. (PLD, PLE and CK3)

As a result, the final VCO output signal is expressed by:

$$f_{VCO} = \left(\frac{160 - N_3}{40} + \frac{N_2}{10000} + \frac{N_1}{2000000}\right) \cdot f_{STD} - f_{CAR1} + f_{CAR2} . (8)$$

According to the values of N1, N2 and N3, a frequency of  $45.08 \sim 75.05$  MHz is generated in 10 Hz steps. If  $f_{CAR1}$  is expressed by N4 and  $f_{CP}$  and  $f_{CAR2}$  by N5,  $f_{VB}$  and  $f_{STD}$  respectively, equation (8) becomes the same as equation (8) provided in "Frequency Configuration".

#### • HET (Heterodyne Oscillator)

The HET oscillator is provided in the PLL unit, which is a PLL circuit (PLL-0) to generate a constant frequency signal of 36.22 MHz. This output signal is connected to the IF unit and supplies the second transmitter/receiver mixer. In FM transmission mode, the audio signal from the microphone is applied to this PLL to yield FM modulation.

PLL-0 consists mainly of IC19. VCO $_0$  is Q29: 2SK192A, locked to 36.22 MHz. A signal of 1/2  $f_{STD}$  (10 MHz) is supplied from the reference frequency generator to IC19, where it is divided to 1/500 to make a 20 kHz comparison output frequency.

The oscillator output of VCO<sub>0</sub> is applied to IC19 via buffer amplifier Q26: 2SC2668 and divided to 1/N0 (1/1811 constant) and the output is phase compared with the 20 kHz reference signal in the phase comparator. This is used to lock the fequency of VCO<sub>0</sub>. NO (1811) is sent from the Digital A unit to the PLL unit. The PLL-0 output is sent to the IF unit via buffer amplifiers Q25: 2SC2668 and Q24: 2SC1907 and an LPF (Low Pass Filter).

#### • CAR1

The CAR1 generator is provided in the digital B (CAR) unit, which makes a signal of approx. 45.5 MHz on the basis of the 9 MHz crystal oscillator and divides it to 1/100 in the PLL-4 circuit to generate a 455 kHz signal. This signal is sent to the IF unit and mixed with the CAR3 signal to becomes a 355 kHz signal. This is sent to the fourth receiver mixer in reception mode. In transmission mode, the signal is sent to the balanced modulator to generate a 455 kHz DSB (Double Side Band) signal.

PLL-4 consists mainly of IC1: MN6147. VCO4 (Q4: 2SC2668) is locked to approx. 45.5 MHz. A 9 MHz signal is supplied from the  $f_{CP}$  oscillator Q1: 2SC2787 to IC1 and divided to 1/1800 to make a 5 kHz comparison output frequency. VCO4 output is applied to IC1 via buffer amplifier Q5: 2SC2668 and divided to 1/N4, and the output is phase compared with the 5 kHz signal and is then used to lock VCO4 in 5 kHz steps. The output signal from PLL4 is divided to 1/100 by IC5: M54459L to become a signal of approx. 455 kHz in 50 Hz steps. This passes through the LPF and is supplied from output buffer Q14/Q15: 2SC2458 to the IF unit as the CAR1 signal.

The non-divided 45.5 MHz signal is applied to the mixer Q18: 3SK73, where the PLL-5 output (the base of CAR2 signal) is added to the signal, and the output is sent to the PLL unit to form a part of the digital VFO.

Thus, the operating frequency is not changed even if the CAR1 frequency is changed, i.e.,  $f_{CP}$  and N4 are optional. When  $f_{CAR1}$  is changed, IF shift is effected in both transmission and reception modes. This characteristic is used to realize USB/LSB mode switching functions,

| Mode  | Basic<br>N4→Slope Tune/CW VBT | CAR1 frequency      |

|-------|-------------------------------|---------------------|

| USB   | 9070 →9039                    | 453.50 kHz → 451.95 |

| LSB   | 9130 →9161                    | 456.50 → 458.05     |

| CW-W  | 9086 →9071                    | 454.30 →453.55      |

| CW-N  | 9100 →9093                    | 455.00 →454.65      |

| AM-W  | 9100 →9069                    | 455.00 →453.45      |

| AM-N  | 9100 →9085                    | 455.00 →454.25      |

| FM    | 9100 → -                      | 455.00 → -          |

| FSK-W | 9144 →9173                    | 457.20 → 458.75     |

| FSK-N | 9144 →9151                    | 457.20 → 457.55     |

Table-2 N4 Data Shift

variable bandwidth, fine adjustment of carrier point, centering CW/FSK signals in the IF bandpass, etc. Fine adjustment of carrier point is provided by trimmer capacitors TC1 (for USB) and TC2 (for LSB) connected to the  $f_{CP}$  crystal oscillator  $\times$ 1. The other functions are executed by controlling N4 from the microprocessor. N4 is sent from the Digital A unit (a part of it is relayed by the PLL unit) as 4 bit serial data. (A0—A3, CL4).

#### • CAR2

The CAR2 circuit is provided in the digital B unit, which generates a signal of approximately 71.5 MHz on the basis of the 9 MHz crystal oscillator. This is divides to 1/100 in the PLL-5 circuit to generate a 9.285 MHz signal. This signal is sent to the IF unit and used as a local oscillation signal for the third receiver mixer in reception mode, and that of the first transmitter mixer in transmission mode. PLL-5 consists mainly of IC2: MN6147.

A 9 MHz signal is supplied from the  $f_{VB}$  oscillator Q6: 2SC2787 to IC1 and divided to 1/1800 to make a 5 kHz comparison output frequency. The output of VCO5, Q9: 2SC2668 is applied to IC2 via buffer amplifier Q10: 2SC2668 and divided to 1/N5, and the output is compared in phase with the 5 kHz signal and used to lock VCO5 to approx. 71.5 MHz in 5 kHz steps. The PLL-5 output signal is divided to 1/100 by IC3: M54459L to become a signal of approx. 715 kHz in 50 Hz steps. It passes through a LPF and goes to IC4: SN16913P, where it is mixed with 1/2 fstd (10 MHz) from the reference frequency generator to become the CAR2 signal at 9.285 MHz. Any mixer spurious components within this signal are eliminated by ceramic filter CF1. The filtered signal is applied to the IF unit via buffer amplifier Q12/Q13: 2SC2458. The 71.5 MHz output signal from PLL-5 is applied to mixer Q18, where the PLL-4 output signal (the basis of the CAR4 signal) is added to the signal, and the output is sent to the PLL unit to form a part of digital VFO. Thus, like CAR1, the operating frequency is not changed even if the CAR2 frequency is changed, i.e., fvB and N5 are optional.

However, if the  $f_{CAR2}$  is changed, IF shift is effected across the 8.83 MHz filter (the second receiver IF filter) in both transmission and reception. (When the  $f_{CAR2}$  is changed, the 455 kHz filter is not shifted.) This characteristic is used to realize the variable bandwidth function.

| Mode  | Basic (units missing)<br>N5→Slope Tune or CW<br>VBT (max) | CAR2 frequency            |   |

|-------|-----------------------------------------------------------|---------------------------|---|

| USB   | 14300 → 14378                                             | 9285.00 kHz → 9281.10 kHz | = |

| LSB   | 14300 →14222                                              | 9285.00 →9288.90          |   |

| CW-W  | 14300 →14362                                              | 9285.00 →9281.90          | _ |

| CW-N  | 14300 →14315                                              | 9285.00 →9284.25          |   |

| AM-W  | 14300 → 14362                                             | 9285.00 →9281.90          | _ |

| AM-N  | 14300 →14330                                              | 9285.00 →9283.50          |   |

| FM    | 14300 → -                                                 |                           |   |

| FSK-W | 14300 →14238                                              | 9285.00 →9288.10          |   |

| FSK-N | 14300 →14285                                              | 9285.00 →9285.75          |   |

Table-3 N5 Data Shift

Initialization of the VBT (Variable Bandwidth Tuning) adjustment (making the band center frequencies of the 8.83 MHz and 455 kHz filters the same) is performed by trimmer capacitor TC3 connected to the fVB crystal oscillator X2. The actual variable bandwidth function is realized by controlling N5 by the microprocessor. N5 is sent from the Digital A unit as A0—A3, and CL5 data.

#### CARφ

CAR0 is a signal of approx. 8.83 MHz, which is derived by subtracting CAR1 from CAR2 in mixer IC6 provided on the CAR unit. Any mixer spurious components generated by IC6: SN16913P are eliminated by ceramic filter CF2. The signal is then applied to both the IF and Control units via Q16: 2SC2787 and Q17: 2SC2458.

The signal applied to the IF unit is used as a transmission carrier in the CW and FM modes. The signal applied to the Control unit is used as the demodulation carrier for the monitor circuit in the SSB and FSK modes.

#### • CAR3

CAR3 on the IF unit generates three different frequencies depending on the mode (100 kHz = CW, AM and FM, 98.5 kHz = USB and 101.5 kHz = LSB and FSK.) These are used as the BFO (Beat Frequency Oscillator) in the SSB and FSK modes, as a side tone generating carrier in the CW mode, and as a local oscillators signal for the fourth receiver mixer after being mixed with the CAR1 signal.

In CAR3, the tuning capacitors for each mode are selected by diode switches D69 and D70. Q33: 3SK92A is the oscillator. The output is supplied from the CAR3 terminal to the side tone generator on the Control unit via buffer amplifier Q32: 2SC2458 and, at the same time, it is mixed with the CAR1 signal from CAR unit in mixer Q34: 3SK73 to generate a local oscillator signal ( $f_{CAR1} - f_{CAR3}$ ) to be applied to the fourth receiver mixer. The output of Q32 is further applied to the SSB and FSK product detectors via buffer amplifiers Q31 and Q14: 2SC2458.

#### CAR4

CAR4 on the IF unit serves as a BFO dedicated to CW demodulation, and as a side tone generating carrier. The oscillator frequency is 99.2 kHz, but it is varied by the CW PITCH control so the receiving pitch can be set to the desired frequency in the CW mode. The CAR4 signal is generated by Q16: 2SK192A and is applied to buffer amplifier Q15: 2SC2458. The output is supplied from the CAR4 terminal to the Control unit generator side tone and, at the same time, it is applied to buffer amplifier Q14 via diode switches D34 and D68 and connects to the CW detector.

#### • Reference frequency generator

The reference frequency *fsrb'* the frequency control base of the TS-940S, is generated by the 20 MHz crystal oscillator X1 and Q1: 2SC2668 on the PLL unit, and further applied to buffer amplifier Q2: 2SC2787. X1 and Q1 are replaceable by the optional TCXO (Temperature Compensated Crystal Oscillator) SO-1.

The output of Q2 is used as the 20 MHz fstd as is. It is also

multiplied three times to provide 60 MHz  $3f_{STD}$ . Further, it is divided to 1/2 by half of IC1: SN74LS73AN to provide 10 MHz 1/2  $f_{STD}$ . This 1/2  $f_{STD}$  is supplied to the CAR unit via buffer amplifier Q4: 2SC2787 as well as being used in the PLL unit. The 1/2  $f_{STD}$  is further divided to 1/2 by the other half of IC1 to provided a 5 MHz 1/4  $f_{STD}$ .

#### AFSK signal and marker signal

A part of the 5 MHz (1/4  $f_{STD}$ ) signal generated by the PLL unit frequency generator reference is applied to 1/5 divider IC2: SN74LS90N to provide a 1 MHz (1/20  $f_{STD}$ ) signal. This signal is applied to programmable divider IC4: MC569BCP. The dividing ratio of this IC is switched between 218/235 interlocked with the FSK key SPACE/MARK setting. The output of IC4 returns to IC2, passes through the 1/2 divider, establishes a 50% duty cycle and is then sent to the microphone amplifier circuit of the IF unit via active LPF Q4: 2SA1115, where it is converted to an FSK modulation signal. The total dividing ratio is 1/8720  $f_{STD}$  (2.2936 kHz) in SPACE and 1/9400  $f_{STD}$  (2.1277 kHz) MARK. The shift width is 165.9 Hz, which is a slight deviation from the standard value, but no problem in practical use.

The carrier frequency and shift width during transmission are the same in accuracy as  $f_{STD}'$  and are very stable. In modes other than FSK, IC4 stops operation and thus, an AFSK signal is not transmitted.

The marker signal chain divides the 1 MHz ( $1/20~f_{STD}$ ) signal from the preceding stage IC2 to 1/10 through IC3: SN74LS90N to generate 100 kHz signals ( $1/200~f_{STD}$ ). When the marker switch is off, IC3 is reset and the operation is stopped.

#### **RECEIVER**

The signal received through the antenna is applied to the RF unit ANT terminal. The signal passes through the transmitter/receiver selector circuit and goes out from the EXT terminal. The output is connected to the RF unit RXA terminal via the selector circuit provided on the rear panel. This signal is applied to the receiver BPF through the RF attenuator (0, 10, 20, or 30 dB selectable) via relays RL1 and RL2. The BPF divides the received frequency range (up to 30 MHz) into nine bands, which are automatically selected by RX BPF control data (RB0—RB3) from the Digital A unit.

| Receive frequency | R   | RX BPF information |     |     |        |  |  |

|-------------------|-----|--------------------|-----|-----|--------|--|--|

| (MHz)             | RΒφ | RB1                | RB2 | RB3 | RX BPF |  |  |

| ~0.5              | 0   | 0                  | 0   | 0   | Α      |  |  |

| 0.5~1.5           | 1   | 0                  | 0   | 0   | В      |  |  |

| 1.5~3             | 0   | 1                  | 0   | 0   | С      |  |  |

| 3~4               | 1   | 1                  | 0   | 0   | D      |  |  |

| 4~7               | 0   | 0                  | 1   | 0   | E      |  |  |

| 7~8.5             | 1   | 0                  | 1   | 0   | F      |  |  |

| 8.5~14            | 0   | 1                  | 1   | 0   | G      |  |  |

| 14~20             | 0   | 0                  | 0   | 1   | Н      |  |  |

| 20~30             | 1   | 1                  | 1   | 0   | Ī      |  |  |

Table-4 Selection of RX BPF

The signal from the BPF runs through the RF AGC circuit composed of PIN diodes D23 and D26: MI204. It is then amplified by RF amplifier comprising Q10: 2SK125 pair and applied to the first receiver mixer Q9: 2SK125 pair, where it is mixed with the VCO signal, and the output is converted to the first IF signal at 45.05 MHz. This signal is applied to the grounded gate post amplifier Q7, 8: 2SK125, and the output is applied from the RIF terminal to IF unit.

The unwanted signal components are eliminated from the 45.05 MHz first IF signal when it passes through the MCF XF1 with 15 kHz bandwidth. The signal is then applied to the second receiver mixer Q4 and Q5: 2SK125, mixed with the HET signal (36.22 MHz) and converted to the second IF signal (8.83 MHz). This signal is separated into two channels: one is supplied to the noise blanker on the Control unit, and the other is applied to the second IF signal filter circuit via the noise blanking gate comprised of diodes D3—D6: 1S1587.

This filter circuit is provided with crystal filter XF2: YK-88S1 with a 2.7 kHz bandwidth for SSB (used also for wide CW/FSK and narrow AM), and wide band LC filters L37, L38 for FM (used also for wide AM when the optional AM filter is not provided.) As an option, the filter circuit permits use of two kinds of filters: a YK-88C-1 with 500 Hz bandwidth for CW and a YK-88A-1 with 6 kHz bandwidth for AM. These four filter types are automatically selected by the W/N-mode information (WN, ND2 and MD1) from the Digital A unit via the keyboard.

| W/N switch | WI            | DE            | NAR           | ROW                           |

|------------|---------------|---------------|---------------|-------------------------------|

| Mode       | 2nd IF filter | 3rd IF filter | 2nd IF filter | 3rd IF filter                 |

| SSB        | 2.7 kHz       | 2.7 kHz       | 2.7 kHz       | 2.7 kHz                       |

| CW, FSK    | 2.7 kHz       | 2.7 kHz       | 0.5kHz*²      | 0.5 kHz*3<br>or<br>0.25 kHz*4 |

| AM         | 6 kHz*1       | 6 kHz         | 2.7 kHz       | 2.7 kHz                       |

| FM         | Wide band     | 6 kHz         | Wide band     | 6 kHz                         |

<sup>\*0: 2.7</sup> kHz+2.7 kHz=2.4 kHz (Total selectivity)

**Table-5 Selection of filters**

The received signal, having passed through the second IF filter, is applied to the third receiver mixer Q7, 8: 3SK73 to be mixed with the CAR2 signal (9.285 MHz) and then converted to the third IF signal (455 kHz). The output is then separated into two channels. One is connected to the Control unit FIN terminal, goes through IF amplifier Q45: 2SC2787 and third IF filter CF1: CFV455F. It is then applied to limiter amplifiers IC11 and IC12: μPC577H for amplitude limiting, and the output is applied to ceramic discriminators L12: CFY455S for FM detection. The detected output is supplied from the FMV terminal to the IF unit or the FM mode signal via the de-emphasis circuit and. at the same time, the noise component near 40 kHz is eliminated. The signal is then connected to the squelch circuit, noise amplifier Q46 and Q47: 2SC2458, noise rectifier D80 and D81: 1SS33 and the comparator

consisting of IC13 2/2: NJM4558S. The above Control unit circuits function not only in the FM mode, but in all modes. Therefore, one noise squelch system is employed in all modes. The squelch control output mutes the IF unit audio amplifier via the MTU terminal. (IF unit Q28) The third IF signal is amplified by Q10: 3SK73 no the IF unit and is then applied to the filter circuit as the third IF signal. This filter circuit is provided with ceramic filter CF1: CFJ455K12 with a 2.7 kHz bandwidth for SSB (used also for wide CW/FSK and narrow AM) and ceramic filter CF2: CFW455HT with a 6 kHz bandwidth for AM wide. As an option, the filter circuit provides for use of either a CW 500 Hz crystal filter: YG-455C-1 or 250 Hz: YG-455CN-1 bandwidth filter. These three filter types are automatically selected by information from the Digital A unit, like the second IF filters. For selection operation data, refer to Table. 5. The signal from the third IF filter is amplified by Q11: 3SK73 and applied to the fourth receiver mixer to be mixed with the 355 kHz (CAR1-CAR3) signal and converted o the fourth IF signal. The output is applied to Q13: 2SK73 via the notch filter circuit. This amplifier output is detected by either the SSB/CW product detector or the AM detector. The detected signal is applied to AF GAIN control via the squelch gate Q28: 2SC2458 and preamplifier Q29: 2SC2459. In CW mode, it is also possible to pass the signal through the AF TUNE circuit, IC1 and IC2: BA718. The output of Q3 is also applied to the AGC circuit. The received AF signal from the AF GAIN control is applied to the Control unit, where it is amplified by the audio power amplifier IC15: HA1368 and used to drive the speaker.

#### Front end

The TS-940S RF circuit has been specifically designed to provide high immunity to strong adjacent signals. The incoming signal from the antenna is first applied to a source follower buffer consisting of two 2SK125s, and then to a balanced mixer (consisting of two 2SK125s) where it is converted to the 45.05 MHz first IF signal. This IF signal is then applied to a grounded gate amplifier-pair. The VCO signal is delivered to the RF unit at low level, and is applied to the balanced mixer after being high-gain amplified. The use of a source follower for the first receiver stage reduces pre-mixer distortion and harmonics to negligible levels.

The junction FET balanced mixer contributes immunity to strong adjacent signals. The amplifier which follows allows low mixer gain. This design practically eliminates mixer saturation.

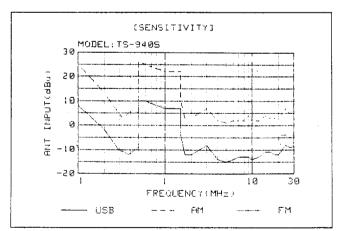

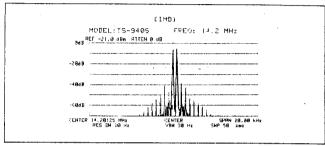

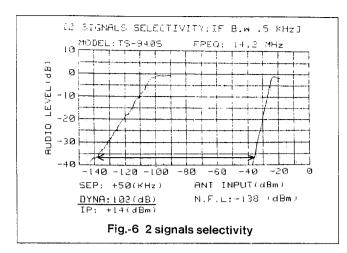

Figure 6 shows the IM (intermodulation) dynamic range characteristic. The characteristic shown was measured with a TS-940S in the CW mode with an optional YG-455C-1 IF filter (center freq.: 455 kHz, bandwidth: 500 Hz) installed. The noise floor level is —138 dB, IM dynamic range is 102 dB, and the intercept point is +14 dB.

<sup>\*1:</sup> option YK-88A-1 installed

<sup>\*3:</sup> option YG-455C-1 installed

<sup>\*2:</sup> option YK-88C-1

<sup>\*4:</sup> option YG-455CN-1

#### Additional receiver circuit

#### Noise blanker (provided on the Control circuit)

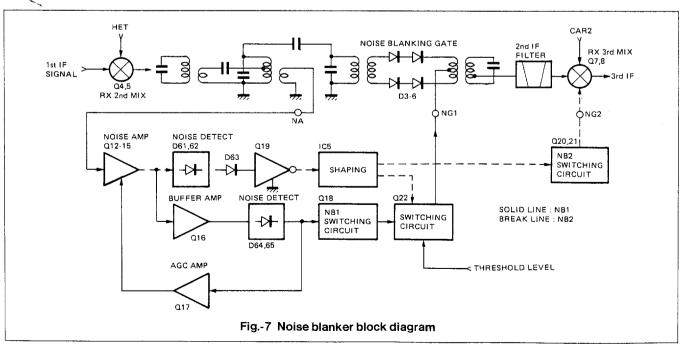

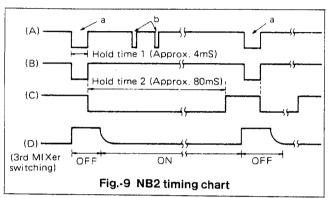

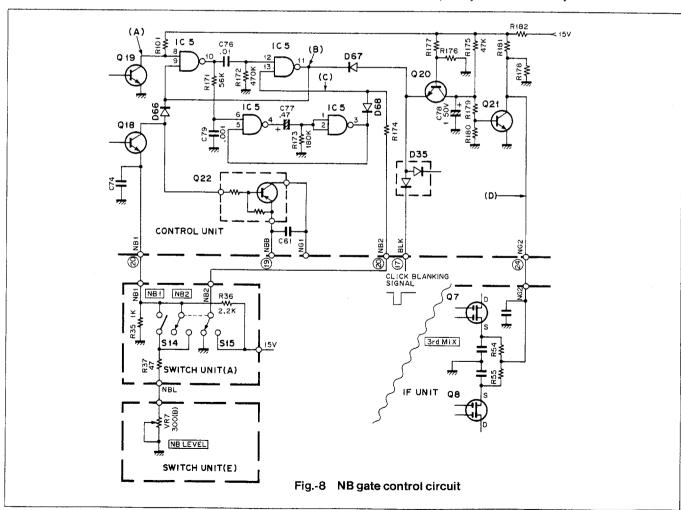

Fig. 7 gives a block diagram of the noise blanker. This circuit is comprised of two channels, NB1 and NB2. The signal taken from the tuned output circuit of the second receiver mixer, comprised of Q4 and Q5 on the IF unit, is supplied from the NA terminal to the Control unit and amplified approx. 70 dB by Q12—Q15.

In the case of the NB1 channel, the noise signal is detected by diodes D64 and D65 through the buffer Q16 and then applied to the switching transistors Q18 and Q22. In the case of the NB2 channel, the noise is directly applied to the noise detector comprising D61 and D62. The NB1 channel takes out only the pulse noise contained in the input signal and switches the noise blanking gate composed of diodes D3—D6, located before the IF unit XF2.

NB1 channel operation is conventional. On the other hand, the noise output detected by D61 and D62 in the NB2 channels is waveform shaped by IC5 after running through D63 and Q19, and only the high level pulse component is taken out as a square wave.

This component is switched by Q18 and in turn is used to switch the NB gate via D66 and Q22. At the same time, it is also used for switching the third receiver mixer Q7, Q8 on the IF unit via Q20 and Q21. The NB2 channel is especially effective for that special noise known as "The woodpecker".

In addition, in the TS-940S, the "click" noise generated when the frequency is changed one step by the digital VFO is eliminated through the NB2 channel by utilizing the BLK signal from the Digital unit. The functions of the NB circuit are described in detail below.

In Fig. 8, Q18 and Q22 form a conventional NB circuit, which controls the NB gate. When the NB1 switch S14 is turned on, Q18 turns on and controls Q22 according to whether or not a pulse noise exists, and opens or closes the NB gate comprising D3—D6 on the IF unit.

NB LEVEL (VR7) varies the operating threshold of Q18 so the NB effect can be varied.

Next, NB2 is explained. When a signal corresponding to a noise is applied to Q19, the collector of Q19 is set to a low level (hereafter abbreviated Lo. (and high level to Hi.) IC5, pins 11 and 9 are Hi, because pin 12 is Lo due to R172. As described above, when the collector (IC5, pin 8) of Q19 becomes Lo, IC5, pin 10 becomes Hi. As pin 10 next becomes Hi, a charging current flows in C176, pin 12 becomes Hi and pins 11 and 9 become Lo, in sequence.

As pin 9 becomes Lo, pin 10 is held Hi. This holding time is determined by the charge constant of C76 and R172, approx. 4 ms. If this time is exceeded, pins 11 and 9 are returned to their initial states, Hi.

During this period, the conventional NB1 channel is operating through D66, and Q27 and Q21 are operating, whereby the third mixer (Q7 and Q8 on the IF unit) is cut off. Even if pins 11 and 9 become Hi, the base voltage of Q21 is in the state of cutting off the charging voltage determined by R175 and C78, and it continuously cuts off the third mixer. This is the control for NB2.

IC5, pin 6 is connected by R171 (56 k  $\Omega$ ) and returned to Hi when the NB2 control time (about 4 ms) elapses. Upon this change from Lo to Hi, a charging current flows in C77 through R178 and changes pins 1 and 2 from Lo to Hi. IC5, pins 3 and 5 become Lo, keeping pin 4 Hi and holding the charging time determined by C77 and R173, approx. 80 ms. During this period, IC5, pin 13 is held Lo (pin 11 is Hi) through D68 so the NB2 does not mis-fire with a normal pulse for approx. 80 ms from the time the first noise pulse goes out, even if a pulse noise is again entered. This is the operation for periodic woodpecker noise. When the NB2 channel is on, conventional noise is also blanked because one pole of S15 operates the NB1 circuit.

#### CW-VBT, SSB-SLOPE-TUNE (RF/IF and PLL/CAR unit)

The TS-940S is equipped with SSB SLOPE TUNE and CW VBT circuits, a notch filter, and an AF TUNE cirucit which operates in the CW mode.

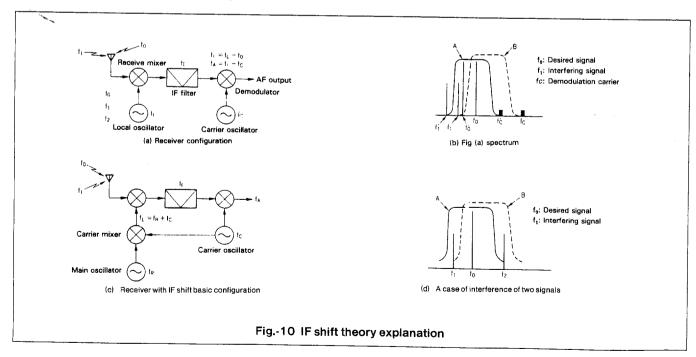

The TS-940S provides the best variable characteristic depending on operating mode and IF bandwidth, using digital technology controlled by microprocessor. In this parented systems, the effective intermediate frequencies of two filters are shifted independently to allow control of the overall bandwidth (U.S. PAT No. 4267605). The principle of the IF shift system is briefly explained below.

Assume that the desired signal  $(f_0)$  and an adjacent signal  $(f_1)$  are input to the receiver. These two signals are converted to the intermediate frequency and applied to the IF filter. If the filter has the selectivity characteristic shown in Figure 10 (b), the adjacent signal passes through the filter and is demodulated, resulting in interference.

If the local oscillator frequency is shifted by  $-\Delta f$ . This is indicated by  $f_0$  and  $f_1$  in Figure 10 (b). In this case, only the desired signal passes through the filter However, the pitch of the demodulated audio signal will change unless the carrier frequency (fc) is shifted by the same amount as

the local oscillator frequency. Otherwise, this would make the demodulated SSB signal unrecongnizable.

With the circuit shown in Figure 10 (c), both the local oscillator and carrier shift together. When the carrier frequency is changed by  $-\Delta f$ , the local oscillator frequency input to the mixer is also changed by an equal amount. In Figure 10 (b), the  $f_0{}'$  and  $f_1{}'$  indicate the same signals as previously described. In this example, however, the carrier frequency is changed from fc to fc'. This is equivalent to shifting the frequency of the filter by  $+\Delta f$  (as indicated by B) without the resultant frequencies of the incoming signals being changed.

The IF shift system avoids interference from adjacent signals by causing an apparent shift in the center frequency of the filter, as shown above.

Assume that there are two adjacent signals as shown in Figure 10 (d). When the filter frequency is as indicated by A, signal  $f_1$  causes interference and, when it is as indicated by B, signal  $f_2$  causes interference. The IF shift system cannot prevent interference when two or more signals are within the filter passband and the desired signal is between them.

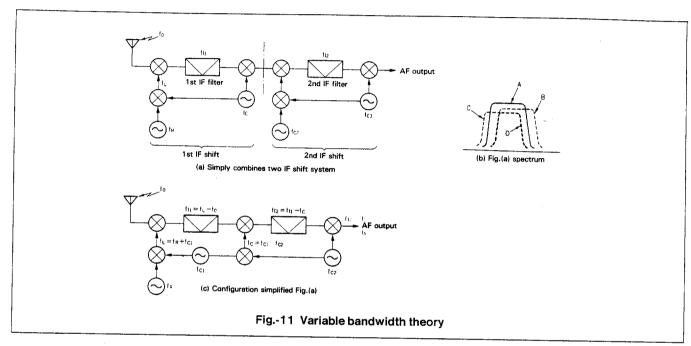

In the new interference reduction system, the apparent center frequencies of two IF filters are shifted independently to vary the overall IF bandwidth.

The circuit shown in Figure 11 (a) simply combines two IF shift systems. This system can narrow the overall IF bandwidth as shown in Figure 11 (b) by independently shifting the carrier oscillator frequencies (fc1 and fc2). In Figure 11 (b), A represents the overall IF frequency response when the apparent frequencies of both the IF filters are equal; at this time, the overall bandwidth is maximum. When the center frequency of the 1st filter is

shifted as indicated by dotted line B (by varying fc1) and that of the 2nd filter is shifted as indicated by C (by varying fc2), the overall IF bandwidth is reduced to that indicated by line D.

Interference caused by two or more adjacent signals, previously discussed and shown in Figure 10 (c) can be reduced by this new cirucit. Practically speaking, however, this circuit configuration is too complex and expensive. A simplified circuit is shown in Figure 11 (c). This circuit operates in the same basic manner as the circuit shown in Figure 11 (a), but the number of mixers and oscillators has been reduced.

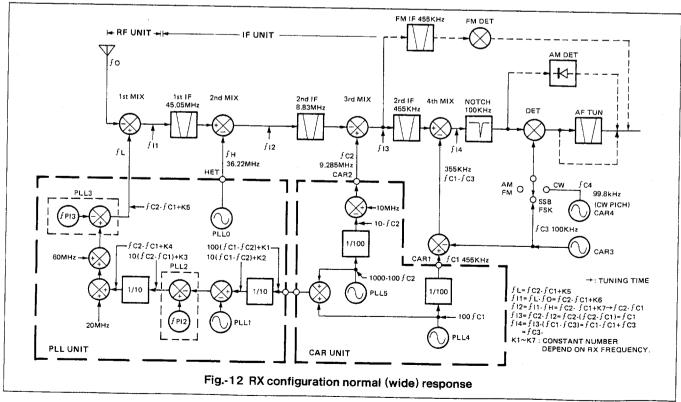

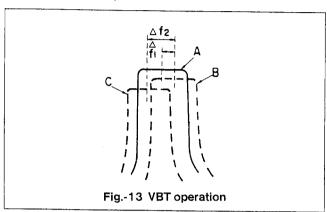

Figure 12 shows the TS-940S "rough" block diagram which is more complex than that shown in Figure 11 (c) because the 1st IF frequency is 45.05 MHz to achieve general coverage, the notch filter circuit is designed to operate independently of the VBT, and a CW pitch control circuit is employed. The 1st IF filter has a bandwidth of 15 kHz and has no influence on the interference reduction system. (In practice, the 1st IF filter has the same apparent center frequency as the 2nd filter, even if the 2nd filter is shifted.) The overall or composite frequency response of the 2nd and 3rd IF stages is as shown by line A in Figure 13 when the CAR1 and CAR2 frequencies are at their normal positions.

Assume that the CAR1 frequency is lowered by  $f_1$  (that is, the VCO frequency  $f_L$  is lowered by  $\triangle f_1$ ) to shift the overall center frequency of the 2nd and 3rd IF stages to the position indicated by dotted line B. The overall bandwidth does not vary at this time. When the CAR2 frequency is lowered by  $\triangle f_2$ , the 2nd filter center frequency is shifted, indicated by C. Thus, the composite IF bandwidth is reduced.

In the TS-940S, CAR1 and CAR2 frequencies are generated by the PLL cirucit and controlled by the microprocessor, and the amount of change  $\Delta f_1$  and  $\Delta f_2$  is digitally tracked, allowing only the bandwidth to narrow without changing the center frequency of composite passband. This is the principle of the CW-VBT feature used in the TS-940S.

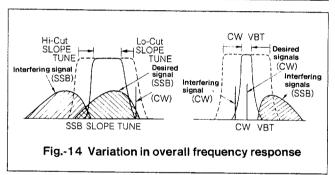

When  $\Delta f_1 = \Delta f_2$ , the low frequency cutoff point is raised, allowing low frequency interference rejection.

The high frequency cutoff can be varied by lowering the CAR2 frequency by  $\Delta f_2$  without changing the CAR1 frequency. With the TS-940S SSB SLOPE TUNE system, these two functions are individually adjustable by separate controls, and correspondence between the function and the control is reversed according to the sideband mode.

These HIGH and LOW CUT controls are concentrically arranged on the front panel and can be easily manipulated. they are audio high and low cut controls.

The SSB SLOPE TUNE system operates in the LSB and USB modes. The CW VBT system operates in the CW, FSK, AM and TUNE modes when all optional filters are installed. When no optional filters are installed, the CW VBT system operates in the CW, FSK and TUNE modes with the filter selector switch placed at WIDE, and in the AM mode with the filter switch placed at NARROW. (For the precise relationship between the optional filters and their interference reduction features, please see the paragraph on filter options.)

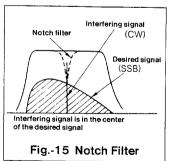

#### Notch filter (provided in the IF unit)

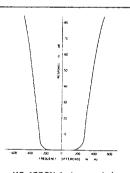

This is a bridge T filter composed of L, C and R elements, which is inserted between the fourth receiver mixer and the 100 kHz IF amplifier Q13. The notch filter, which has the sharp characteristic that provides attenuation on the order of 40 dB to the interfering signal shown in Fig. 15. It varies the voltage applied to the cathode of varicap diode D38, thereby changing the resonant frequency. The notch filter functions in all modes except FM.

Fig.-16 AF tune operation

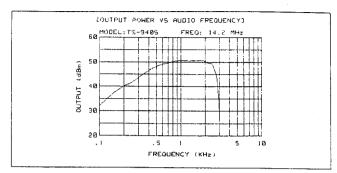

#### • AF-TUNE (provided on the IF unit)

Figure 16 illustrates the principle of the AF TUNE feature, which reduces interfering signals and white noise.